- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371771 > HB28L064MM3 (Renesas Technology Corp.) MultiMediaCard 32 MByte/64 MByte/128 MByte/256 MByte/512 MByte PDF資料下載

參數(shù)資料

| 型號: | HB28L064MM3 |

| 廠商: | Renesas Technology Corp. |

| 英文描述: | MultiMediaCard 32 MByte/64 MByte/128 MByte/256 MByte/512 MByte |

| 中文描述: | 多媒體32 MByte/64 MByte/128 MByte/256 MByte/512字節(jié) |

| 文件頁數(shù): | 77/91頁 |

| 文件大?。?/td> | 526K |

| 代理商: | HB28L064MM3 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁當前第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁

HB28K032/L064/J128/J256/J512MM3, HB28K032/L064/J128/J256RM3

Rev.0.02, Sep.15.2004, page 77 of 89

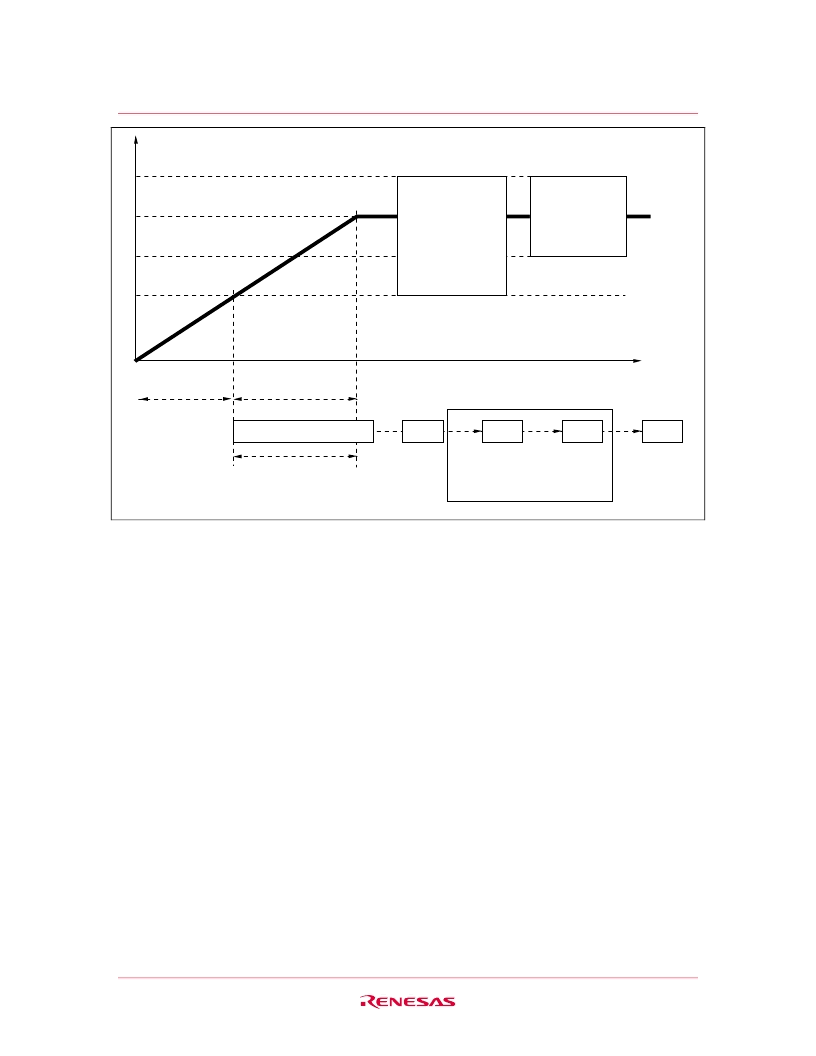

Initialization delay: The maximum of

1 msec, 74 clock cycles and supply

ramp up time

CMD1

CMD1

CMD1

CMD2

Optional repetitions of CMD1

until no cards are responding

with busy bit set.

3.6 V

2.0 V

2.7 V

Bus master supply voltage

Card logic working

voltage range

Memory field

working voltage

range

Power up time

Supply ramp up time

N

CC

N

CC

N

CC

Initialization sequence

Time

Power-up Diagram

After power up (including hot insertion, i.e. inserting a card when the bus is operating) the

MultiMediaCard enters the idle state. During this state the MultiMediaCard ignores all bus transactions

until CMD1 is received.

CMD1 is a special synchronization command used to negotiate the operation voltage range and to poll

the cards until they are out of their power-up sequence. Besides the operation voltage pro-file of the

cards, the response to CMD1 contains a busy flag, indicating that the card is still working on its power-

up procedure and is not ready for identification. This bit informs the host that at least one card is not

ready. The host has to wait (and continue to poll the cards) until this bit is cleared.

Getting individual cards, as well as the whole MultiMediaCard system, out of idle state is up to the

responsibility of the bus master. Since the power up time and the supply ramp up time depend on

application parameters such as the maximum number of MultiMediaCards, the bus length and the

power supply unit, the host must ensure that the power is built up to the operating level (the same level

which will be specified in CMD1) before CMD1 is transmitted.

After power up the host starts the clock and sends the initializing sequence on the CMD line. This

sequence is a contiguous stream of logical

‘

1

’

s. The sequence length is the maximum of 1 msec, 74

clocks or the supply-ramp-up-time; The additional 10 clocks (over the 64 clocks after what the card

should be ready for communication) are provided to eliminate power-up synchronization problems.

When the power is on after the power down, V

CC

must be 0.25 V or less.

相關PDF資料 |

PDF描述 |

|---|---|

| HB28J512MM3 | MultiMediaCard 32 MByte/64 MByte/128 MByte/256 MByte/512 MByte |

| HB3104AD | 128Kx8 EEPROM |

| HB3104AL | 128Kx8 EEPROM |

| HI3104AL | 128Kx8 EEPROM |

| HI3104AP | 128Kx8 EEPROM |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| HB2A102K-S265B | 制造商:Hitano Enterprise Corp 功能描述:Bulk |

| HB2A102K-S565B | 制造商:Hitano Enterprise Corp 功能描述:Bulk |

| HB2A103K-S565B | 制造商:Hitano Enterprise Corp 功能描述: |

| HB2A122K-S265B | 制造商:Hitano Enterprise Corp 功能描述: |

| HB2A122K-S565B | 制造商:Hitano Enterprise Corp 功能描述:Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。