- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370400 > GTLPH16612DL 18-Bit Bus Transceiver PDF資料下載

參數(shù)資料

| 型號: | GTLPH16612DL |

| 元件分類: | 電平轉(zhuǎn)換器 |

| 英文描述: | 18-Bit Bus Transceiver |

| 中文描述: | 18位總線收發(fā)器 |

| 文件頁數(shù): | 2/14頁 |

| 文件大小: | 112K |

| 代理商: | GTLPH16612DL |

Philips Semiconductors

Product data

GTLPH16612

18-bit GTLP to LVTTL/TTL bidirectional

universal translator (3-State)

2

2001 Sep 28

853–2285 27174

FEATURES

18-bit bidirectional bus interface

Translates between GTLP logic levels (B ports) and LVTTL/TTL

logic levels (A ports)

Edge rate control circuitry on the Bn outputs rising/falling edges to

minimize system noise in a multipoint backplane environment

5 V I/O tolerant on the LVTTL side

No bus current loading when LVTTL output is tied to 5 V bus

3-State buffers

Output capability: +64 mA/-32 mA on the LVTTL side; +40 mA on

the GTLP side

LVTTL input levels on control pins

Power-up reset

Power-up 3-State

Positive edge triggered clock inputs

Latch-up protection exceeds 500 mA per JESD78

ESD protection exceeds 2000 V HBM per JESD22-A114,

200 V MM per JESD22-A115 and 750 V (Bn I/O exceeds 1000 V)

CDM per JESD22-C101

DESCRIPTION

The GTLPH16612 is a high-performance BiCMOS product designed

for V

CC

operation at 3.3V with I/O compatibility up to 5 V.

The GTLPH16612 is unique in that pin 50 is a no connect and this

device can be used as a replacement device in sockets where

pin 50 is 3.3/5 V V

CC

or 3.3 V BIAS V

CC

.

This device is an 18-bit universal transceiver featuring non-inverting

3-State bus compatible outputs in both send and receive directions.

Data flow in each direction is controlled by output enable (OEAB and

OEBA), latch enable (LEAB and LEBA), and clock (CPAB and

CPBA) inputs. For A-to-B data flow, the device operates in the

transparent mode when LEAB is High. When LEAB is Low, the A

data is latched if CPAB is held at a High or Low logic level. If LEAB

is Low, the A-bus data is stored in the latch/flip-flop on the

Low-to-High transition of CPAB. When OEAB is Low, the outputs are

active. When OEAB is High, the outputs are in the high-impedance

state. The clocks can be controlled with the clock-enable inputs

(CEBA/CEAB).

Data flow for B-to-A is similar to that of A-to-B but uses OEBA,

LEBA and CPBA.

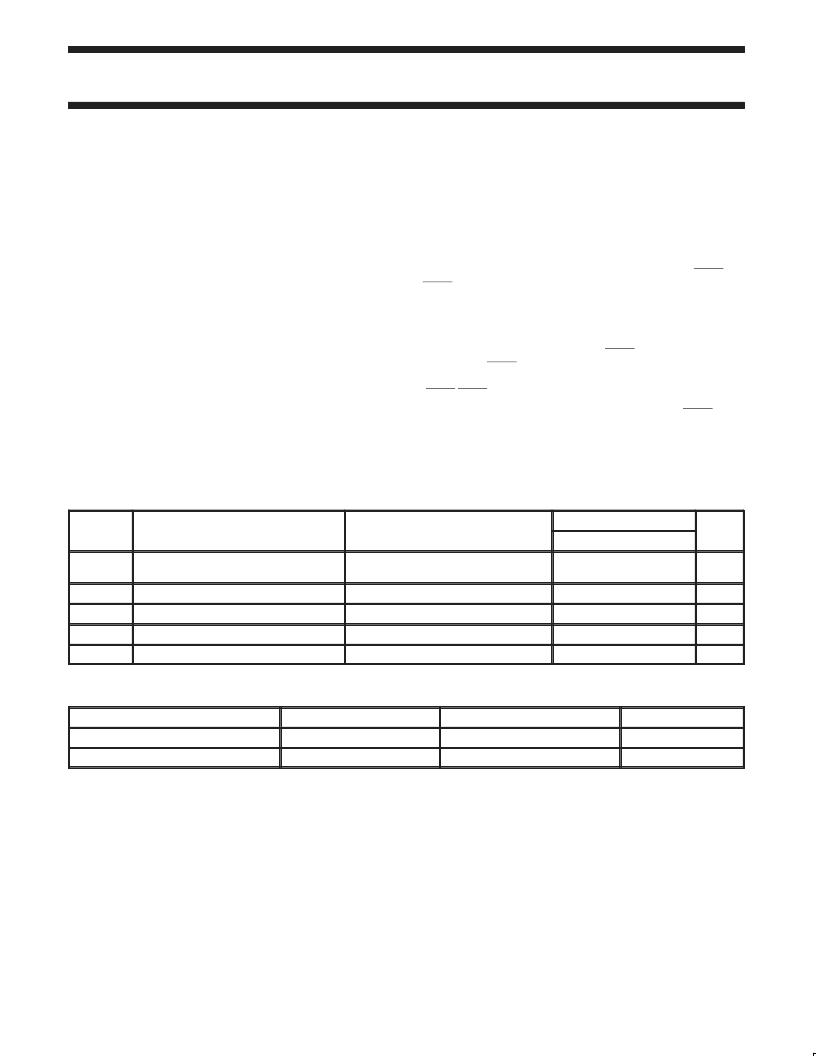

QUICK REFERENCE DATA

SYMBOL

PARAMETER

CONDITIONS

T

amb

= 25

°

C

TYPICAL

UNIT

3.3 V

t

PLH

t

PHL

Propagation delay

An to Bn or Bn to An

C

L

= 50 pF

1.9

ns

C

IN

Input capacitance (Control pins)

V

I

= 0 V or V

CC

4

pF

C

I/O

An I/O pin capacitance

V

I/O

= 0 V or V

CC

9

pF

C

I/O

Bn I/O pin capacitance

V

I/O

= 0 V or 1.5 V

5.3

pF

I

CCZ

Total supply current

Outputs disabled

12

mA

ORDERING INFORMATION

PACKAGES

TEMPERATURE RANGE

ORDER CODE

DWG NUMBER

56-Pin Plastic SSOP

–40 to +85

°

C

GTLPH16612DL

SOT371-1

56-Pin Plastic TSSOP

NOTE:

1. Standard packing quantities and other packaging data is available at

www.philipslogic.com/support/packages

.

–40 to +85

°

C

GTLPH16612DGG

SOT364-1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GTL | |

| GTM415-F | Modem Controller |

| GTM415-T | Modem Controller |

| GTR2-12-60 | Analog IC |

| GTR2-15-60 | Analog IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GTLPH16927 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:18-BIT LVTTL-TO-GTLP BUS TRANSCEIVER WITH SOURCE-SYNCHRONOUS CLOCK OUTPUTS |

| GT-LT1000 | 制造商:Stellar Labs Power 功能描述:Gateway Replacement Laptop Battery |

| GT-LT2113U | 制造商:Stellar Labs Power 功能描述:Gateway Replacement Laptop Battery |

| GTM1000C2 | 制造商:HellermannTyton 功能描述:Grip Tie mount used for .75 wide Grip Ties - Black |

| GTM10080 | 制造商:Red Lion Controls 功能描述:10" DISPLAY 8 TANK |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。