- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄239070 > GS88218BD-150VT (GSI TECHNOLOGY) 512K X 18 CACHE SRAM, 7.5 ns, PBGA165 PDF資料下載

參數(shù)資料

| 型號(hào): | GS88218BD-150VT |

| 廠商: | GSI TECHNOLOGY |

| 元件分類(lèi): | SRAM |

| 英文描述: | 512K X 18 CACHE SRAM, 7.5 ns, PBGA165 |

| 封裝: | 13 X 15 MM, 1 MM PITCH, FPBGA-165 |

| 文件頁(yè)數(shù): | 2/35頁(yè) |

| 文件大?。?/td> | 1164K |

| 代理商: | GS88218BD-150VT |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)

GS88218/36B(B/D)-xxxV

Rev: 1.04 6/2007

10/35

2002, GSI Technology

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

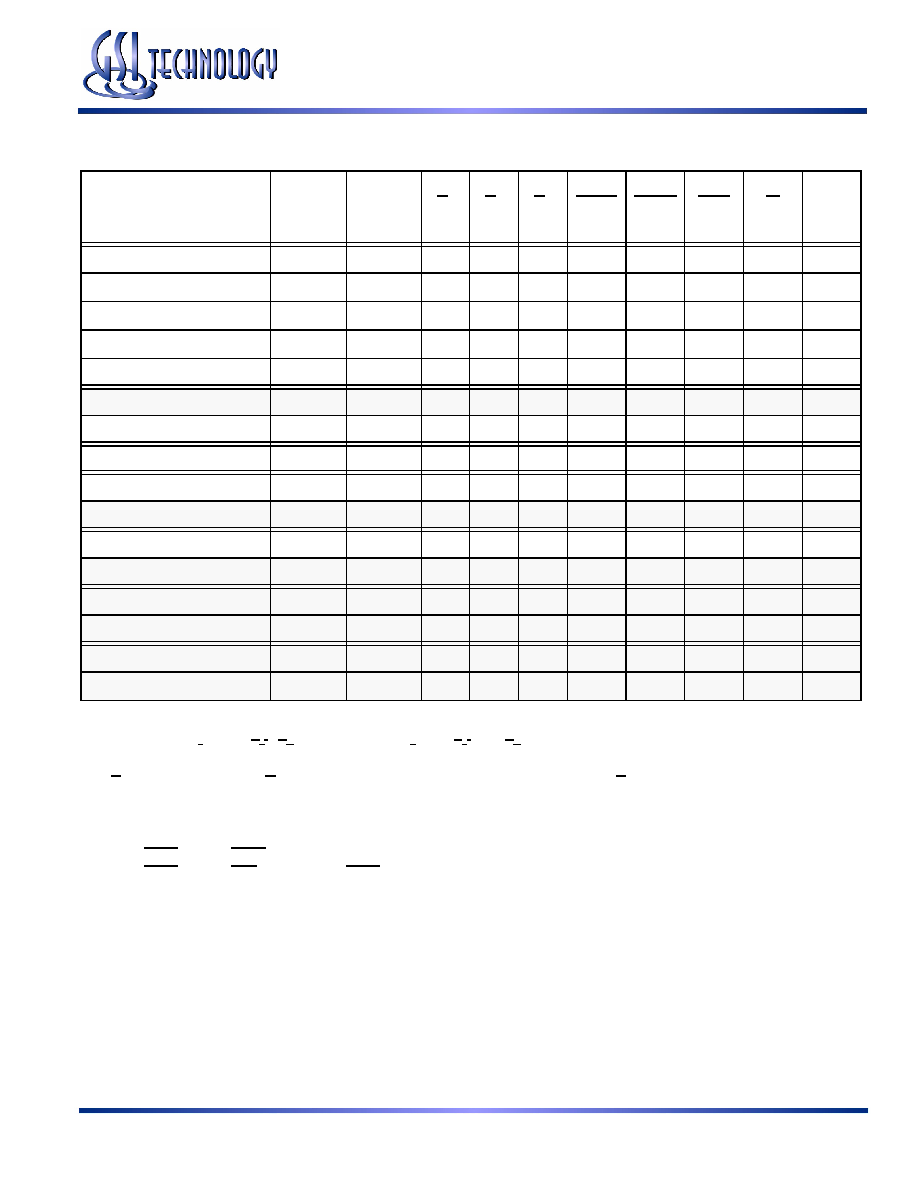

Synchronous Truth Table

Operation

Address

Used

State

Diagram

Key

E1

E2

E3

ADSP ADSC

ADV

W

DQ3

Deselect Cycle, Power Down

None

X

L

X

H

X

L

X

High-Z

Deselect Cycle, Power Down

None

X

L

X

L

X

High-Z

Deselect Cycle, Power Down

None

X

L

X

H

L

X

High-Z

Deselect Cycle, Power Down

None

X

L

X

L

X

High-Z

Deselect Cycle, Power Down

None

X

H

X

L

X

High-Z

Read Cycle, Begin Burst

External

R

L

H

L

X

Q

Read Cycle, Begin Burst

External

R

L

H

L

H

L

X

F

Q

Write Cycle, Begin Burst

External

W

L

H

L

H

L

X

T

D

Read Cycle, Continue Burst

Next

CR

X

H

L

F

Q

Read Cycle, Continue Burst

Next

CR

H

X

H

L

F

Q

Write Cycle, Continue Burst

Next

CW

X

H

L

T

D

Write Cycle, Continue Burst

Next

CW

H

X

H

L

T

D

Read Cycle, Suspend Burst

Current

X

H

F

Q

Read Cycle, Suspend Burst

Current

H

X

H

F

Q

Write Cycle, Suspend Burst

Current

X

H

T

D

Write Cycle, Suspend Burst

Current

H

X

H

T

D

Notes:

1. X = Don’t Care, H = High, L = Low

2. E = T (True) if E2 = 1 and E1 = E3 = 0; E = F (False) if E2 = 0 or E1 = 1 or E3 = 1

3. W = T (True) and F (False) is defined in the Byte Write Truth Table preceding.

4. G is an asynchronous input. G can be driven high at any time to disable active output drivers. G low can only enable active drivers (shown

as “Q” in the Truth Table above).

5. All input combinations shown above are tested and supported. Input combinations shown in gray boxes need not be used to accomplish

basic synchronous or synchronous burst operations and may be avoided for simplicity.

6. Tying ADSP high and ADSC low allows simple non-burst synchronous operations. See BOLD items above.

7. Tying ADSP high and ADV low while using ADSC to load new addresses allows simple burst operations. See ITALIC items above.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GS88218BD-200V | 512K X 18 CACHE SRAM, 6.5 ns, PBGA165 |

| GLCB36D-4Q04 | SNAP ACTING/LIMIT SWITCH, SPDT, MOMENTARY, 0.5A, 120VDC, PANEL MOUNT-THREADED |

| GSCC01A1B-1Q02 | SNAP ACTING/LIMIT SWITCH, SPDT, MOMENTARY, 0.55A, 125VDC, 53.5mm, PANEL MOUNT |

| GSCC01A1B-Q01 | SNAP ACTING/LIMIT SWITCH, SPDT, MOMENTARY, 0.55A, 125VDC, 53.5mm, PANEL MOUNT |

| GLCB03A1B5C024 | SNAP ACTING/LIMIT SWITCH, SPDT, MOMENTARY, 0.55A, 125VDC, PANEL MOUNT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GS88218CB-200 | 制造商:GSI Technology 功能描述:SRAM SYNC DUAL 2.5V/3.3V 9MBIT 512KX18 6.5NS/3NS 119FPBGA - Trays |

| GS88218CB-200I | 制造商:GSI Technology 功能描述:SRAM SYNC DUAL 2.5V/3.3V 9MBIT 512KX18 6.5NS/3NS 119FPBGA - Trays |

| GS88218CB-200IV | 制造商:GSI Technology 功能描述:SRAM SYNC DUAL 1.8V/2.5V 9MBIT 512KX18 6.5NS/3NS 119FPBGA - Trays |

| GS88218CB-200V | 制造商:GSI Technology 功能描述:SRAM SYNC DUAL 1.8V/2.5V 9MBIT 512KX18 6.5NS/3NS 119FPBGA - Trays |

| GS88218CB-250 | 制造商:GSI Technology 功能描述:SRAM SYNC DUAL 2.5V/3.3V 9MBIT 512KX18 5.5NS/2.5NS 119FPBGA - Trays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。