- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370388 > GS82032Q66 x32 Fast Synchronous SRAM PDF資料下載

參數(shù)資料

| 型號: | GS82032Q66 |

| 英文描述: | x32 Fast Synchronous SRAM |

| 中文描述: | X32號,快速同步SRAM |

| 文件頁數(shù): | 5/23頁 |

| 文件大?。?/td> | 649K |

| 代理商: | GS82032Q66 |

Rev: 1.08 2/2001

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

5/23

2000, Giga Semiconductor, Inc.

GS82032AT/Q-200/180/166/133/100

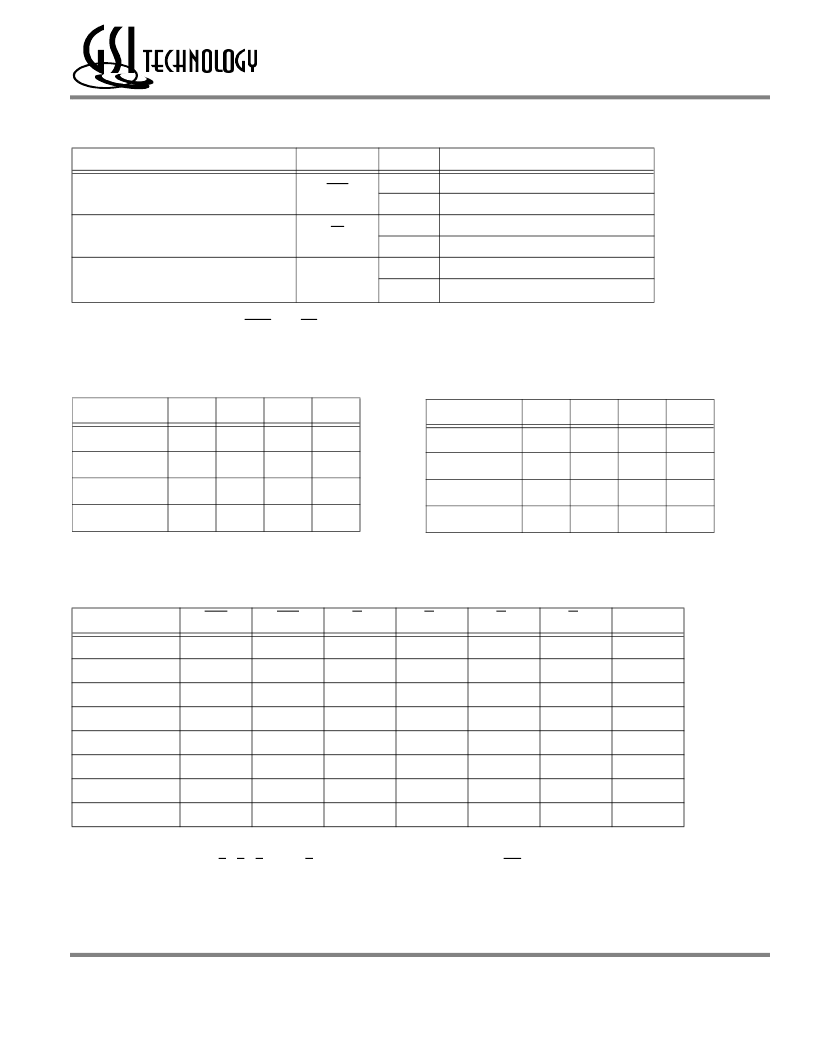

Mode Pin Functions

Note:

There are pull-up devices on LBO and FT pins and a pull-down device on the ZZ pin, so those input pins can be

unconnected and the chip will operate in the default states as specified in the above table.

Burst Counter Sequences

Linear Burst Sequence

Byte Write Truth Table

Notes:

1.

2.

3.

All byte outputs are active in read cycles regardless of the state of Byte Write Enable inputs.

Byte Write Enable inputs B

A

, B

B

, B

C

and/or B

D

may be used in any combination with BW to write single or multiple bytes.

All byte I/Os remain High-Z during all write operations regardless of the state of Byte Write Enable inputs.

Mode Name

Pin Name

State

L

H or NC

L

H or NC

L or NC

Function

Linear Burst

Interleaved Burst

Flow Through

Pipeline

Active

Standby, I

DD

= I

SB

Burst Order Control

LBO

Output Register Control

FT

Power Down Control

ZZ

H

Function

GW

BW

B

A

B

B

B

C

B

D

Notes

Read

H

H

X

X

X

X

1

Read

H

L

H

H

H

H

1

Write byte

A

H

L

L

H

H

H

2, 3

Write byte

B

H

L

H

L

H

H

2, 3

Write byte

C

H

L

H

H

L

H

2, 3, 4

Write byte

D

H

L

H

H

H

L

2, 3, 4

Write all bytes

H

L

L

L

L

L

2, 3, 4

Write all bytes

L

X

X

X

X

X

Note: The burst counter wraps to initial state on the 5th clock

.

I

nterleaved Burst Sequence

Note: The burst counter wraps to initial state on the 5th clock.

A[1:0]

A[1:0]

A[1:0]

A[1:0]

1st address

00

01

10

11

2nd address

01

10

11

00

3rd address

10

11

00

01

4th address

11

00

01

10

A[1:0]

A[1:0]

A[1:0]

A[1:0]

1st address

00

01

10

11

2nd address

01

00

11

10

3rd address

10

11

00

01

4th address

11

10

01

00

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GS82032Q66I | x32 Fast Synchronous SRAM |

| GS82032T100 | x32 Fast Synchronous SRAM |

| GS82032T100I | x32 Fast Synchronous SRAM |

| GS82032T117 | x32 Fast Synchronous SRAM |

| GS82032T117I | x32 Fast Synchronous SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GS82032Q-66 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64K x 32 2M Synchronous Burst SRAM |

| GS82032Q66I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x32 Fast Synchronous SRAM |

| GS82032Q-6I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64K x 32 2M Synchronous Burst SRAM |

| GS82032T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64K x 32 2M Synchronous Burst SRAM |

| GS82032T/Q-150/138/133/117/100/66 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64K x 32 2M Synchronous Burst SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。