- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67672 > GP1R (Mitel Networks Corporation) Dual Mode CDMA/AMPS Baseband Interface PDF資料下載

參數(shù)資料

| 型號(hào): | GP1R |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | Dual Mode CDMA/AMPS Baseband Interface |

| 中文描述: | 雙模式CDMA / AMPS二元基帶接口 |

| 文件頁(yè)數(shù): | 8/15頁(yè) |

| 文件大?。?/td> | 139K |

| 代理商: | GP1R |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)當(dāng)前第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)

2

PLUTO

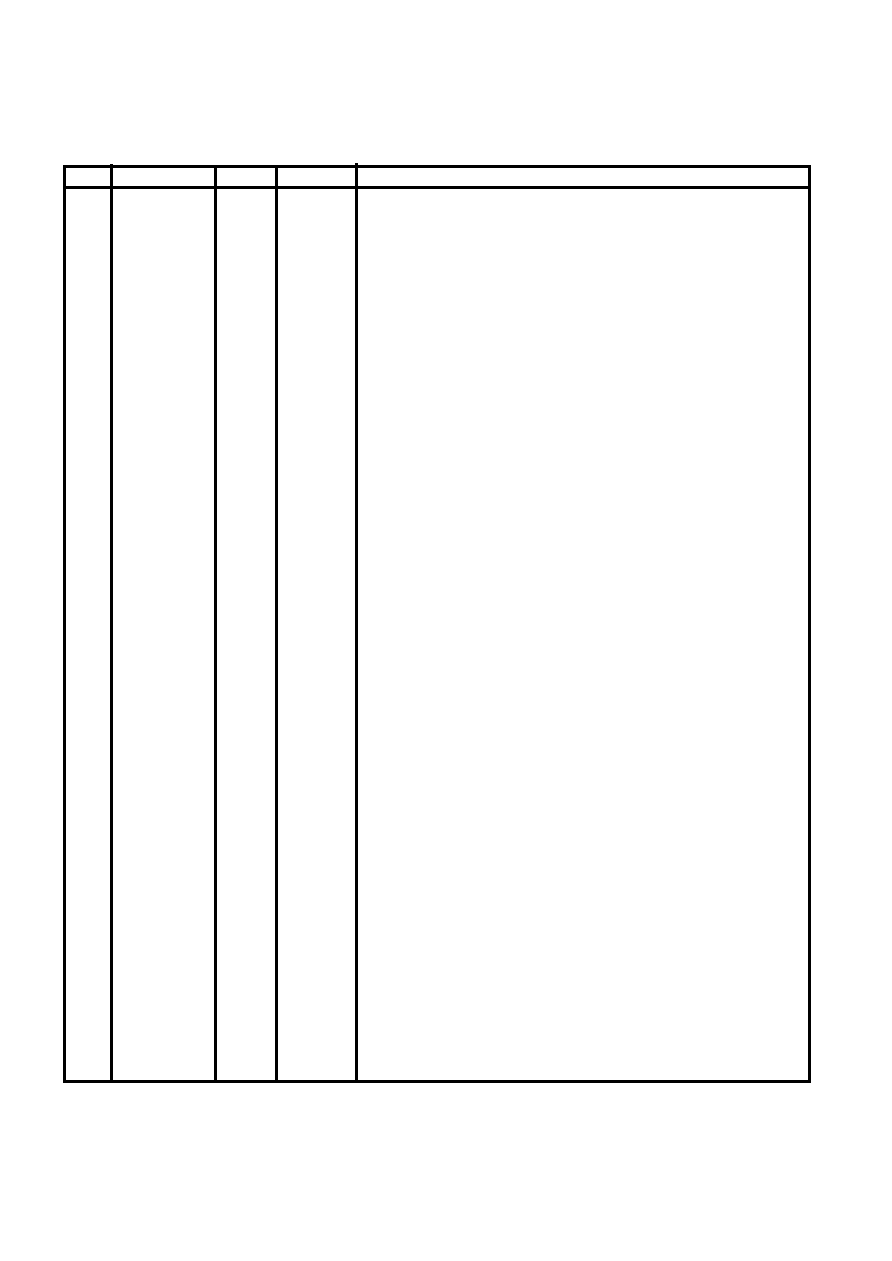

PIN DESCRIPTION

No

Pin Name

Type

A/D

Description

1

VDD

Power

Power Supply

2

RSET

Input

Analog

Bias current setting resistor - 40k

to ground

3

GND

Ground

4

TX_IF

Input

Analog

TX VCO output

5

IDLEB

Digital

Idle mode control signal - active low - pulled low if left unconnected

6

PD TX

Output

TX synthesiser charge pump output

7

FMB

Input

Digital

FM mode control signal - active low - pulled low if left unconnected

8

PD_RX

Output

Analog

RX synthesiser charge pump output

9

SLEEPB

Input

Digital

Sleep mode control signal - active low - pulled low if left unconnected

10

RX_IF

Input

Analog

RX VCO output

11

TX_LOCK

Output

Digital

TX synthesiser lock detect open drain output - pulled high by ext. resistor

12

RX_LOCK

Output

Digital

RX synthesiser lock detect open drain output - pulled high by ext. resistor

13

TCXO/4

Output

Digital

TCXO divided by 4 output

14

TXD<0>

Input

Digital

Transmit data bit 0 (lsb)

15

TXD<1>

Input

Digital

Transmit data bit 1

16

TXD<2>

Input

Digital

Transmit data bit 2

17

TXD<3>

Input

Digital

Transmit data bit 3

18

TXD<4>

Input

Digital

Transmit data bit 4

19

TXD<5>

Input

Digital

Transmit data bit 5

20

TXD<6>

Input

Digital

Transmit data bit 6

21

TXD<7>

Input

Digital

Transmit data bit 7 (MSB)

22

TXCLK

Input

Digital

Complimentary Transmit Clock (+ve)

23

TXCLKB

Input

Digital

Complementary Transmit Clock (-ve)

24

CHIPx8

Input

Digital

9.8304MHz synthesiser output

25

VDD

Power

Power Supply

26

TCXO

Input

Analog

TCXO 19.68MHz a.c. coupled sinewave input

27

GND

Ground

28

SUB

Ground

Substrate-Ground

29

RESET

Input

Digital

Chip master reset - pulled high if not connected

30

SDATA

Input

Digital

Serial Interface Data Input

31

SCLK

Input

Digital

Serial Interface Clock Input

32

SLATCH

Input

Digital

Serial Interfce Latch Input

33

S<0>

Input

Digital

Aux ADC mux channel select LSB

34

n/c

35

RXID<0>

Output

Digital

I-Channel RX CDMA output LSB - low when inactive

36

RXID<1>

Output

Digital

I-Channel RX CDMA output bit 1 - low when inactive

37

RXID<2>

Output

Digital

I-Channel RX CDMA output bit 2 - low when inactive

38

RXID<3>

Output

Digital

I-Channel RX CDMA output bit 3 - low when inactive

39

S<1>

Input

Digital

Aux ADC mux channel select MSB

40

n/c

41

RXQD<0>

Output

Digital

Q_Channel RX CDMA output LSB - low when inactive

42

RXQD<1>

Output

Digital

Q_Channel RX CDMA output bit 1 - low when inactive

43

RXQD<2>

Output

Digital

Q_Channel RX CDMA output bit 2 - low when inactive

44

RXQD<3>

Output

Digital

Q_Channel RX CDMA output bit 3 - low when inactive

45

GND

Ground

46

VDD

Power

Power Supply

47

RXFMSTB

input

Digital

Receive data FM strobe - pulled low if not connected

48

FMCLK

Input

Digital

Receive data FM clock - pulled low if not connected

49

RXQFMDATA

Output

Digital

Q-Channel RX FM data serial output - low when inactive

50

RXIFMDATA

Output

Digital

I-Channel RX FM data serial output -low when inactive

51

ADCLK

Output

Digital

Auxiliary ADC serial data clock. Low when inactive

52

ADCDATA

Output

Digital

Auxiliary ADC serial data output. Low when inactive

53

ADCENA

Input

Digital

Auxiliary ADC enable - pull down if not used

54

SUB

Ground

Substrate - Ground

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GP2000 | () |

| GP2010 | GPS Receiver RF Front End |

| GP2010 | GPS Receiver RF Front End(用于全球定位系統(tǒng)(GPS)接收器的第二代RF前端) |

| GP2015 | Aluminum Electrolytic Radial Leaded Low Profile Wide Temp Capacitor; Capacitance: 22uF; Voltage: 25V; Case Size: 5x9 mm; Packaging: Bulk |

| GP2015 | GPS Receiver RF Front End(用于全球定位系統(tǒng)(GPS)接收器的第二代RF前端) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GP1R11D5000 | 制造商:Coto Technology 功能描述: |

| GP1R21A0000 | 制造商:SRC Devices 功能描述: |

| GP1R21AD000 | 制造商:SRC Devices 功能描述: |

| GP1S01 | 制造商:SHARP 制造商全稱:Sharp Electrionic Components 功能描述:HIGH SPEED PHOTOINTERRUPTER |

| GP1S01F | 制造商:SHARP 制造商全稱:Sharp Electrionic Components 功能描述:HIGH SPEED PHOTOINTERRUPTER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。