- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370366 > GMS81C5024-XXXPL MICROCONTROLLER|8-BIT|CMOS|LDCC|44PIN|PLASTIC PDF資料下載

參數(shù)資料

| 型號(hào): | GMS81C5024-XXXPL |

| 英文描述: | MICROCONTROLLER|8-BIT|CMOS|LDCC|44PIN|PLASTIC |

| 中文描述: | 單片機(jī)| 8位|的CMOS | LDCC | 44PIN |塑料 |

| 文件頁(yè)數(shù): | 67/93頁(yè) |

| 文件大小: | 853K |

| 代理商: | GMS81C5024-XXXPL |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)當(dāng)前第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)

GMS81C1404/GMS81C1408

June. 2001 Ver 1.2

65

19. Power Saving Mode

For applications where power consumption is a critical

factor, device provides two kinds of power saving func-

tions, STOP mode and Wake-up Timer mode.

The power saving function is activated by execution of

STOP instruction after setting the corresponding status

(WAKEUP) of CKCTLR.

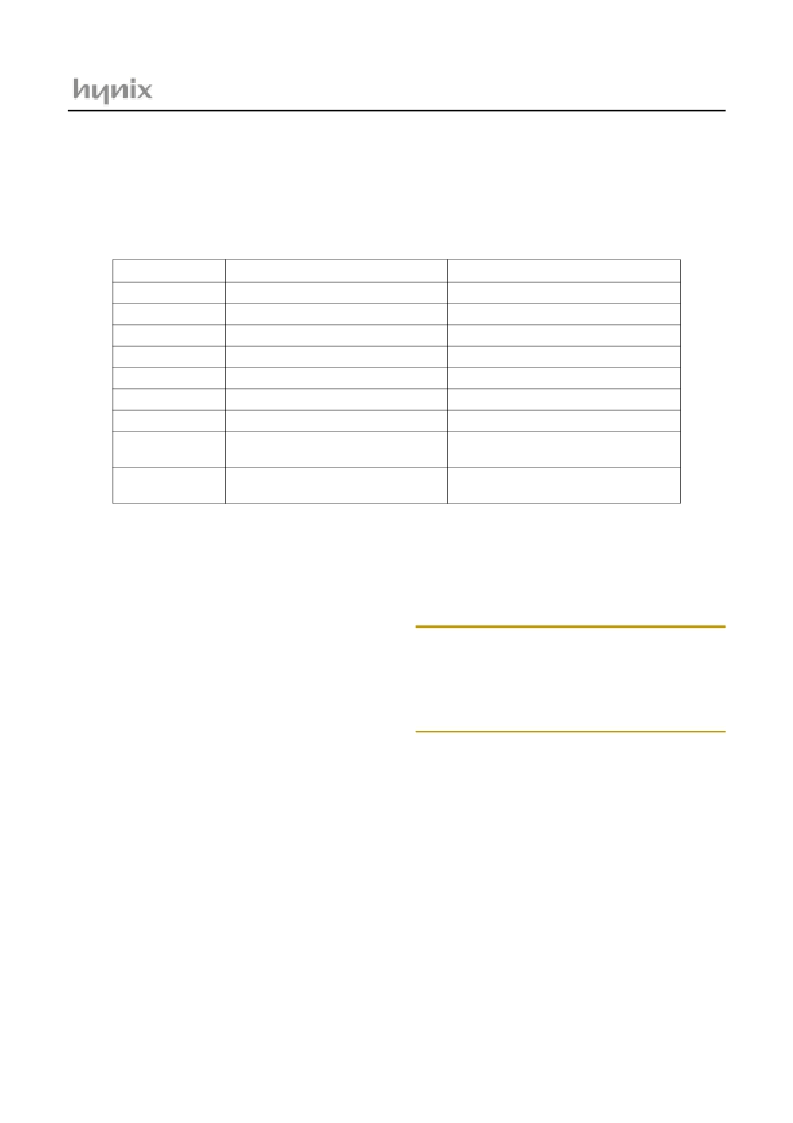

Table 19-1 shows the status of each Power Saving Mode.

19.1 Stop Mode

In the Stop mode, the on-chip oscillator is stopped. With

the clock frozen, all functions are stopped, but the on-chip

RAM and Control registers are held. The port pins out the

values held by their respective port data register, port di-

rection registers. Oscillator stops and the systems internal

operations are all held up.

The states of the RAM, registers, and latches valid

immediately before the system is put in the STOP

state are all held.

The program counter stop the address of the

instruction to be executed after the instruction

“STOP” which starts the STOP operating mode.

The Stop mode is activated by execution of STOP in-

struction after clearing the bit WAKEUP of CKCTLR

to “0”. (This register should be written by byte opera-

tion. If this register is set by bit manipulation instruc-

tion, for example “set1” or “clr1” instruction, it may be

undesired operation)

In the Stop mode of operation, V

DD

can be reduced to min-

imize power consumption. Care must be taken, however,

to ensure that V

DD

is not reduced before the Stop mode is

invoked, and that V

DD

is restored to its normal operating

level, before the Stop mode is terminated.

The reset should not be activated before V

DD

is restored to

its normal operating level, and must be held active long

enough to allow the oscillator to restart and stabilize.

Note:

After STOP instruction, at least two or more NOP in-

struction should be written

Ex)

LDM

CKCTLR,#0000_1110B

STOP

NOP

NOP

In the STOP operation, the dissipation of the power asso-

ciated with the oscillator and the internal hardware is low-

ered; however, the power dissipation associated with the

pin interface (depending on the external circuitry and pro-

gram) is not directly determined by the hardware operation

of the STOP feature. This point should be little current

flows when the input level is stable at the power voltage

level (V

DD

/V

SS

); however, when the input level gets high-

er than the power voltage level (by approximately 0.3 to

0.5V), a current begins to flow. Therefore, if cutting off the

output transistor at an I/O port puts the pin signal into the

high-impedance state, a current flow across the ports input

transistor, requiring to fix the level by pull-up or other

means.

Peripheral

Wake-up Timer

RAM

Retain

Retain

Control Registers

Retain

Retain

I/O Ports

Retain

Retain

CPU

Stop

Stop

Timer0, Timer2

Stop

Operation

Oscillation

Stop

Oscillation

Prescaler

Stop

÷

2048 only

Entering Condition

[WAKEUP]

0

1

Release Sources

RESET, RCWDT, INT0~3,

EC0~1, SPI

RESET, RCWDT, INT0~3,

EC0~1, SPI, TIMER0, TIMER2

Table 19-1 Power Saving Mode

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GMS81C5024-XXXPLT | MICROCONTROLLER|8-BIT|CMOS|LDCC|44PIN|PLASTIC |

| GMS81C5024-XXXQ | MICROCONTROLLER|8-BIT|CMOS|QFP|44PIN|PLASTIC |

| GMS81C5024-XXXQT | MICROCONTROLLER|8-BIT|CMOS|QFP|44PIN|PLASTIC |

| GMS81C5024-XXXSK | Pwr Inductor, Non-Shielded |

| GMS81C5032-XXX | MICROCONTROLLER|8-BIT|CMOS|DIP|40PIN|PLASTIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GMS81C5024-XXXPLT | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROCONTROLLER|8-BIT|CMOS|LDCC|44PIN|PLASTIC |

| GMS81C5024-XXXQ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROCONTROLLER|8-BIT|CMOS|QFP|44PIN|PLASTIC |

| GMS81C5024-XXXQT | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROCONTROLLER|8-BIT|CMOS|QFP|44PIN|PLASTIC |

| GMS81C5024-XXXSK | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MICROCONTROLLER|8-BIT|CMOS|DIP|28PIN|PLASTIC |

| GMS81C5032 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:8-BIT SINGLE CHIP MICROCONTROLLERS |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。