- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370354 > GMM27333230ATG-7K x72 SDRAM Module PDF資料下載

參數(shù)資料

| 型號(hào): | GMM27333230ATG-7K |

| 英文描述: | x72 SDRAM Module |

| 中文描述: | x72內(nèi)存模塊 |

| 文件頁數(shù): | 4/14頁 |

| 文件大?。?/td> | 169K |

| 代理商: | GMM27333230ATG-7K |

Rev. 1.1/Dec.99

4

GMM27333230ATG

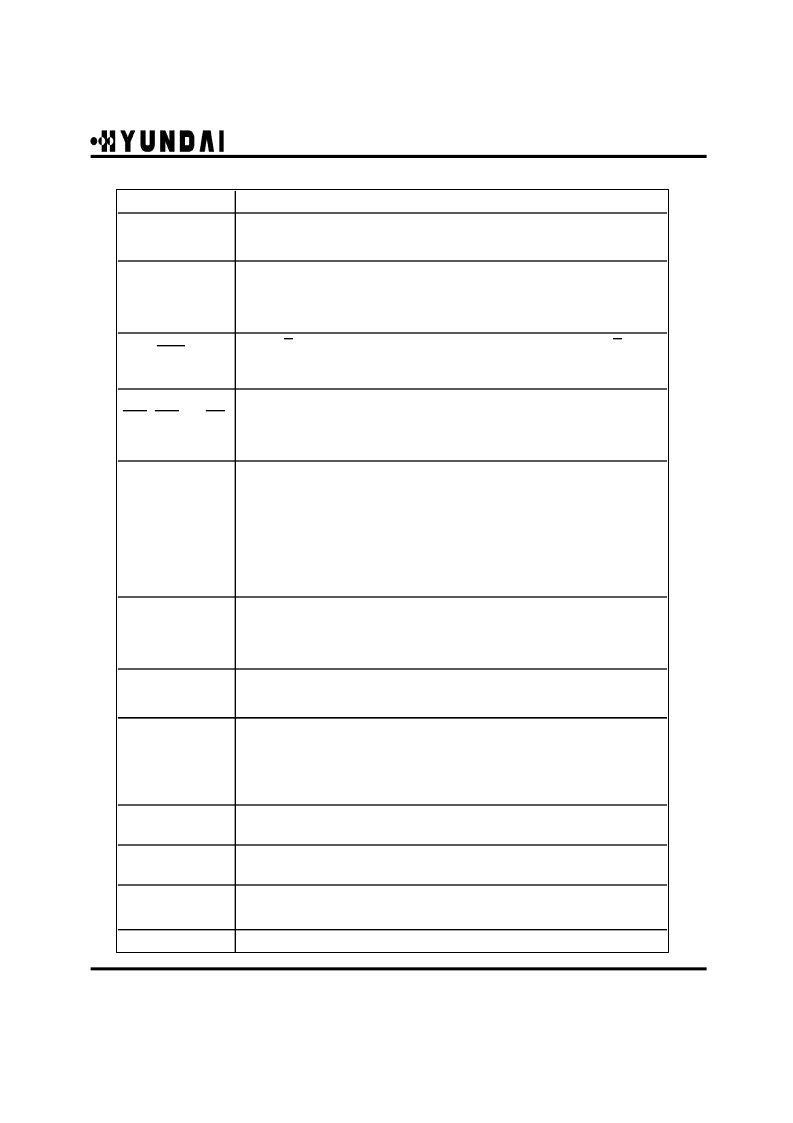

Pin Description

Pin Name

CK0, 1, 2, 3

(input pins)

DESCRIPTION

CK is the master clock input to this pin. The other input signals are

referred at CK rising edge.

CKE0

(input pin)

This pin determines whether or not the next CK is valid. If CKE is

High, the next CK rising edge is valid. If CKE is Low, the next CK

rising edge is invalid. This pin is used for power-down and clock

suspend modes.

When S is Low, the command input cycle becomes valid. When S is

high, all inputs are ignored. However, internal operations (bank active,

burst operations, etc.) are held.

S0, 2

(input pins)

Although these pin names are the same as those of conventional

DRAMs, they function in a different way. These pins define operation

commands (read, write, etc.) depending on the combination of their

voltage levels. For details, refer to the command operation section.

RAS, CAS and WE

(input pins)

A0 ~ A11

(input pins)

Row address (AX0 to AX11) is determined by A0 to A11 level at the

bank active command cycle CK rising edge. Column address is

determined by A0 to A9 and A11 level at the read or write command

cycle CK rising edge. And this column address becomes burst access

start address. A10 defines the precharge mode. When A10 = High at the

precharge command cycle, both banks are precharged. But when A10 =

Low at the precharge command cycle, only the bank that is selected by

BA0 is precharged.

BA0,1

(input pin)

BA0,1 are bank select signal. If BA0 is Low and BA1 is High, bank 0 is

selected. If BA0 is High and BA1 is Low, bank 1 is selected. If BA0 is

Low and BA1 is High, bank 2 is selected. If BA0 is High and BA1 is

High, bank 3 is selected.

DQ0 ~ DQ63

CB0 ~ CB7

(I/O pins)

Data is input and output from these pins. These pins are the same as

those of a conventional DRAMs. Data is not latched in the register.

DQMB0 ~ DQMB7

(input pins)

DQMB controls input/output buffers.

Read operation: If DQMB is High, The output buffer becomes High-Z.

If the DQMB is Low, the output buffer becomes Low-Z.

Write operation: If DQMB is High, the previous data is held (the new data

is not written). If DQMB is Low, the data is written.

V

CC

(power supply pins)

3.3 V is applied. (V

CC

is for the internal circuit)

V

SS

(power supply pins)

Ground is connected. (V

SS

is for the internal circuit)

NC

No Connection pins.

REGE

If REGE input is high, permits the DIMM to operate in `registered mode`.

If REGE input is low, permits the DIMM to operate in `buffered mode`.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GMM2739230ETG-8 | x72 SDRAM Module |

| GMM2739233ETG | 8Mx72|3.3V|75/7K|x9|SDR SDRAM - Unbuffered DIMM 64MB |

| GMM2739233ETG-7 | x72 SDRAM Module |

| GMM2739233ETG-75 | x72 SDRAM Module |

| GMM2739233ETG-7J | x72 SDRAM Module |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GMM27333230ATG-8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x72 SDRAM Module |

| GMM27333233ANTG-10K | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x72 SDRAM Module |

| GMM27333233ANTG-75 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x72 SDRAM Module |

| GMM27333233ANTG-7J | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x72 SDRAM Module |

| GMM27333233ANTG-7K | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x72 SDRAM Module |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。