- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370311 > GD16546B-48BA CLOCK/DATA RECOVERY|BIPOLAR|QFP|48PIN|PLASTIC PDF資料下載

參數(shù)資料

| 型號: | GD16546B-48BA |

| 英文描述: | CLOCK/DATA RECOVERY|BIPOLAR|QFP|48PIN|PLASTIC |

| 中文描述: | 時鐘/數(shù)據(jù)恢復(fù)|雙極| QFP封裝| 48PIN |塑料 |

| 文件頁數(shù): | 5/12頁 |

| 文件大?。?/td> | 145K |

| 代理商: | GD16546B-48BA |

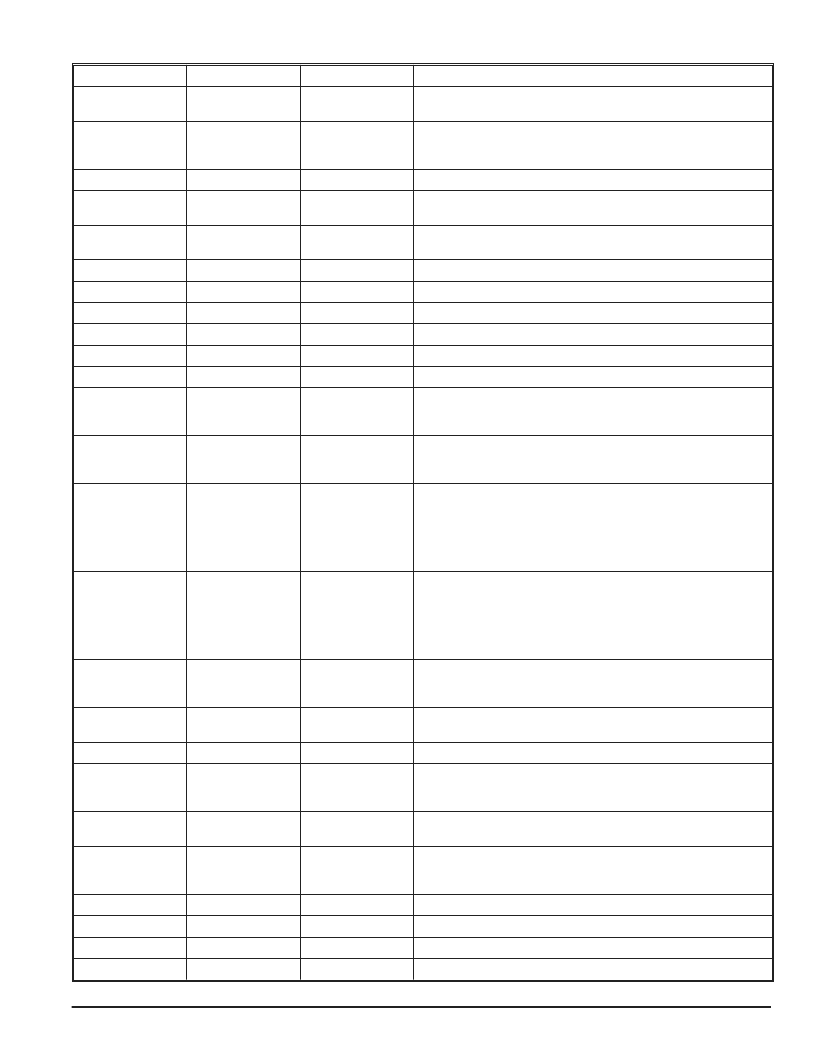

Pin List

Mnemonic:

Pin no.:

Pin Type:

Description:

SDIP, SDIN

8, 6

CML IN

Differential AC or DC coupled (2.5 Gbit/s, 1.25 Gbit/s, 655 Mbit/s

or 155 Mbit/s) Data input.

DIREF, DIREFN

9, 5

Termination

Termination for SDIP and SDIN. Normally terminated with 50

through 47 nF. For DC connected inputs connect to reference

voltage via 50

.

SLBIP, SLBIN

11, 10

CML IN

Differential Loop-Back Data inputs.

SDOP, SDON

28, 29

CML OUT

Data output, differential (2.5 Gbit/s, 1.25 Gbit/s, 655 Mbit/s or

155 Mbit/s), with internal 50

back termination.

SCOP, SCON

31, 32

CML OUT

Clock output, differential (2.5 Gbit/s, 1.25 Gbit/s, 655 Mbit/s or

155 Mbit/s), with internal 50

back termination.

RCIP, RCIN

17, 18

PECL IN

Differential 155.52 MHz or 38.88 MHz reference clock input.

DEC_ADJ

1

ANL IN

Decision level adjust.

VCTL

45

ANL IN

VCO voltage control input.

MON

48

ANL OUT

Input data level monitor output.

MON_REF

47

ANL OUT

Data level monitor reference voltage.

PCTL

41

ANL OUT

Charge pump control.

REF_SEL

20

LVTTL IN

Reference CLK Frequency Select.

0

155.52 MHz

1

38.88 MHz

CDR_SEL

15

LVTTL IN

Clock and Data recovery set-up.

0

Auto lock, 500 ppm.

1

Manual Phase Freq. detector PFC.

BRS0, BRS1

39, 40

LVTTL IN

Multi-rate Data input select.

BRS0

BRS1

0

0

0

1

1

0

1

1

Input

1.25 Gbit/s

155 Mbit/s

622 Mbit/s

2.5 Gbit/s

SBER0, SBER1

25, 26

LVTTL IN

BER select inputs.

SBER0 SBER1

0

0

0

1

1

0

1

1

0.5

×

10

-3

1

×

10

-3

2

×

10

-3

4

×

10

-3

SDOWN_L

22

LVTTL IN

SDOWN_L output disable select pin 1. Outputs set to logic 1

(SDOP=1 SDON=0) when pin set to VCC and LOCK_DET is

asserted.

SDOWN_G

21

LVTTL IN

SDOWN_G output disable select pin 2. Outputs set to logic 1

(SDOP=1 SDON=0) when pin set to VCC.

TCK

38

LVPECL IN

Leave open for normal operation. Only used at DC test.

SD_SEL

13

LVTTL IN

Data input Loop-Back or Limiting amplifier select

0

Loop-Back inputs

1

Limiting Amplifier inputs

SELTCK

36

LVTTL IN

Test-clock select. Connect to VCC for normal operation. Only

used for test purposes.

LOCK_DET

14

PCMOS OUT

Valid data loss alarm output. Asserted when the divided VCO fre-

quency deviates more than 500 ppm from reference frequency, or

BC_DET asserted(, or LOS_DET asserted (

–

bonding option)).

LOS_DET

35

PCMOS OUT

Loss Of Signal alarm output.

BC_DET

23

PCMOS OUT

Bit consecutive detect output.

VEE

16, 27, 33

PWR

Negative supply voltage.

VEEL

4, 7

PWR

Negative supply for Limiting Amplifier.

Data Sheet Rev.: 21

GD16522

Page 5 of 12

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GD16547-48BA | CLOCK/DATA RECOVERY|BIPOLAR|QFP|48PIN|PLASTIC |

| GD16591A-48BA | Telecommunication IC |

| GD16592A-48BA | Telecommunication IC |

| GD16K-DIE | ASIC |

| GC25K-DIE | ASIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GD16547-48BA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CLOCK/DATA RECOVERY|BIPOLAR|QFP|48PIN|PLASTIC |

| GD16557 | 制造商:GIGA 功能描述: |

| GD16571 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:2.5 GBIT/S RETIMING LASER DRIVER |

| GD16571-32BA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:2.5 GBIT/S RETIMING LASER DRIVER |

| GD16585-EB | 制造商:GIGA 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。