- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄370305 > GAL22V10-30LVI Electrically-Erasable PLD PDF資料下載

參數(shù)資料

| 型號(hào): | GAL22V10-30LVI |

| 英文描述: | Electrically-Erasable PLD |

| 中文描述: | 電可擦除可編程邏輯器件 |

| 文件頁(yè)數(shù): | 11/18頁(yè) |

| 文件大小: | 223K |

| 代理商: | GAL22V10-30LVI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)當(dāng)前第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)

Specifications

GAL22LV10

11

f

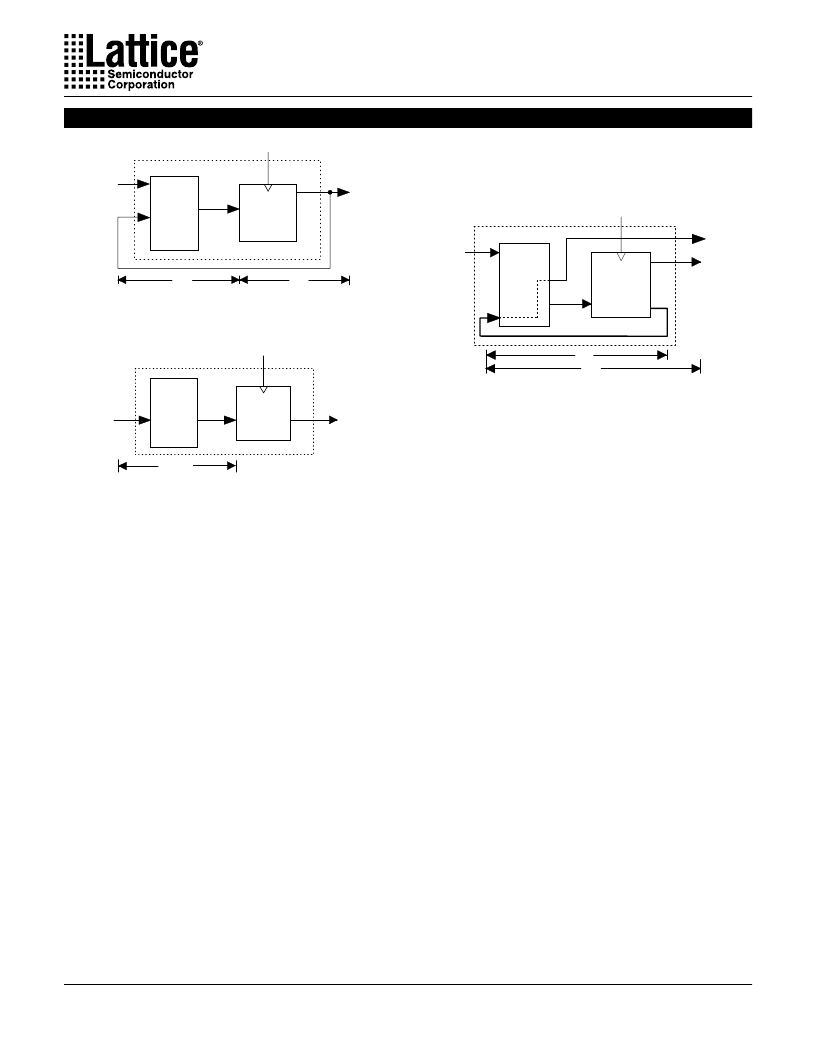

max with Internal Feedback 1/(

t

su+

t

cf)

Note:

t

cf is a calculated value, derived by subtracting

t

su from

the period of fmax w/internal feedback (

t

cf = 1/

f

max -

t

su). The

value of

t

cf is used primarily when calculating the delay from

clocking a register to a combinatorial output (through registered

feedback), as shown above. For example, the timing from clock

to a combinatorial output is equal to

t

cf +

t

pd.

f

max with No Feedback

Note:

f

max with no feedback may be less than 1/(

t

wh +

t

wl). This

is to allow for a clock duty cycle of other than 50%.

REGISTER

LOGIC

ARRAY

t

co

t

su

CLK

f

max with External Feedback 1/(

t

su+

t

co)

Note:

f

max with external feedback is calculated from measured

t

su and

t

co.

REGISTER

LOGIC

ARRAY

CLK

t

su +

t

h

CLK

REGISTER

LOGIC

ARRAY

t

cf

t

pd

f

max Descriptions

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GAL22V10D-7LJI | High Performance E2CMOS PLD Generic Array Logic |

| GAL22V10C-7LJI | MR Series Rocker, 1 lamp circuit (Clear Red) miniature rectangle housing, SPDT, 2 position, Quick-connect, Snap-in panel, Silver alloy contacts |

| GAL22V10D-10QJ | Programmable Logic Controller; Leaded Process Compatible:No; Peak Reflow Compatible (260 C):No |

| GAL22V10D-10QP | High Performance E2CMOS PLD Generic Array Logic |

| GAL22V10D-15LJ | PCB; Leaded Process Compatible:No; PCB Type:4 Channel I/O Rack; Peak Reflow Compatible (260 C):No; Size:3.5 x 3.5 in; Thickness:2.32" RoHS Compliant: No |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GAL22V10-30LVM | 制造商:NSC 制造商全稱(chēng):National Semiconductor 功能描述:GENERIC ARRAY LOGIC |

| GAL22V10B10LJ | 制造商:LATTICE 功能描述:* |

| GAL22V10B-10LJ | 制造商:LATTICE 制造商全稱(chēng):Lattice Semiconductor 功能描述:High Performance E2CMOS PLD Generic Array Logic |

| GAL22V10B10LP | 制造商:LATTICE 功能描述:* |

| GAL22V10B-10LP | 制造商:Lattice Semiconductor Corporation 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。