- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382968 > FS6330-01 (Electronic Theatre Controls, Inc.) LAN HUB CLOCK GENERATOR IC PDF資料下載

參數(shù)資料

| 型號: | FS6330-01 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | LAN HUB CLOCK GENERATOR IC |

| 中文描述: | 局域網(wǎng)集線器時鐘發(fā)生器IC |

| 文件頁數(shù): | 1/6頁 |

| 文件大小: | 68K |

| 代理商: | FS6330-01 |

AMERICAN MICROSYSTEMS, INC.

May 2000

This document contains information on a preproduction product. Specifications and information herein are subject to change without notice.

ISO9001

5.23.00

FS6330

LAN Hub Clock Generator IC

Preliminary Information

1.0 Features

Develops all the high-speed clocks required for LAN

Hub applications

Clock skew on CLKB1:4 clocks < 250ps

Period jitter: 150ps pk-pk typical

Available in 20-pin SSOP and TSSOP packages

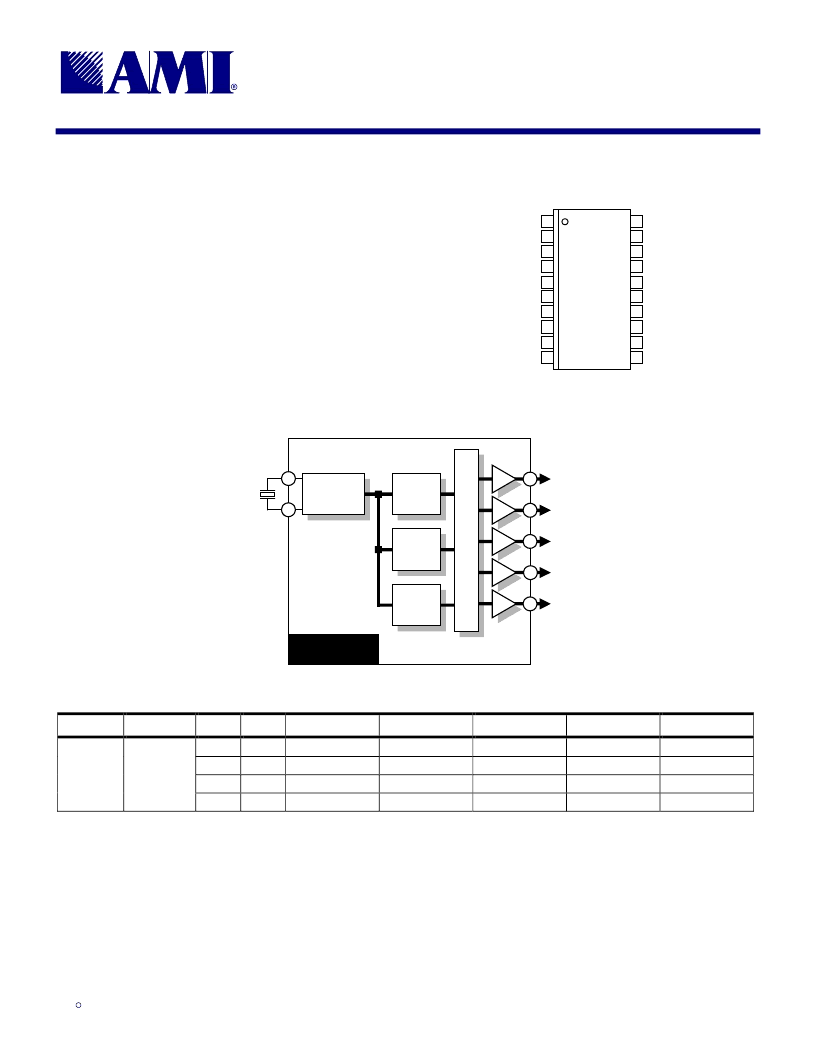

Figure 2: Pin Configuration

X1

VDD

CLKF

SEL1

CLKG

VSS

VDD

X2/REFIN

VSS

SEL0

1

12

2

3

4

5

6

7

8

11

VDD

9

10

CLKB4

VDD

CLKB3

F

VSS

CLKA

CLKB2

CLKB1

VSS

16

15

14

13

20

19

18

17

CLKC

Figure 1: Block Diagram

C

Crystal

Oscillator

FS6330

CLKA

X2/REFIN

X1

PLL

1

PLL

2

PLL

3

CLKB1:4

CLKC

CLKF

CLKG

Table 1: Frequency Table

FONT

CRYSTAL

SEL1

SEL0

CLKA

CLKB[1:4]

CLKC

CLKF

CLKG

0

0

25.000MHz

50.000MHz

66.667MHz

100.000MHz

125.000MHz

0

1

25.000MHz

50.000MHz

75.000MHz

125.000MHz

125.000MHz

1

0

25.000MHz

50.000MHz

83.333MHz

125.000MHz

125.000MHz

FS6330-01

25MHz

1

1

25.000MHz

50.000MHz

100.000MHz

100.000MHz

125.000MHz

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FS6370-01 | EEPROM Programmable 3-PLL Clock Generator IC |

| FS7-4 | Flow Switches - Liquid |

| FS7-4D | Flow Switches - Liquid |

| FS7-4DF | Flow Switches - Liquid |

| FS7-4DS | Flow Switches - Liquid |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FS6370 | 制造商:ONSEMI 制造商全稱:ON Semiconductor 功能描述:EEPROM Programmable 3-PLL Clock Generator IC |

| FS6370-01 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EEPROM Programmable 3-PLL Clock Generator IC |

| FS6370-01G-XTD | 功能描述:時鐘發(fā)生器及支持產(chǎn)品 EE PROG 3-PLL CLOCK RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| FS6370-01G-XTP | 功能描述:時鐘發(fā)生器及支持產(chǎn)品 EE PROG 3-PLL CLOCK RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| FS6377 | 制造商:ONSEMI 制造商全稱:ON Semiconductor 功能描述:Programmable 3-PLL Clock Generator IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。