- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375847 > FM25C160ULEN (FAIRCHILD SEMICONDUCTOR CORP) SERIAL EEPROM|2KX8|CMOS|DIP|8PIN|PLASTIC PDF資料下載

參數(shù)資料

| 型號(hào): | FM25C160ULEN |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | DRAM |

| 英文描述: | SERIAL EEPROM|2KX8|CMOS|DIP|8PIN|PLASTIC |

| 中文描述: | 2K X 8 SPI BUS SERIAL EEPROM, PDIP8 |

| 封裝: | PLASTIC, DIP-8 |

| 文件頁數(shù): | 9/11頁 |

| 文件大?。?/td> | 102K |

| 代理商: | FM25C160ULEN |

9

www.fairchildsemi.com

FM25C160U Rev. B

F

The FM25C160U is also capable of a 16 byte PAGE WRITE

operation. Page write is performed similar to byte write operation

described above. During a Page write operation, after the first byte

of data, additional bytes (up to 15 bytes) can be input, before

bringing the /CS pin high to start the programming. After receipt of

each byte of data, the EEPROM internally increments the four low

order address bits (A3-A0) by one. The high order address bits

(A10-A4) will remain constant. If the master should transmit more

than 16 bytes of data, the address counter (A3-A0) will

“

roll over

”

and the previously loaded data will be reloaded. See Figure11.

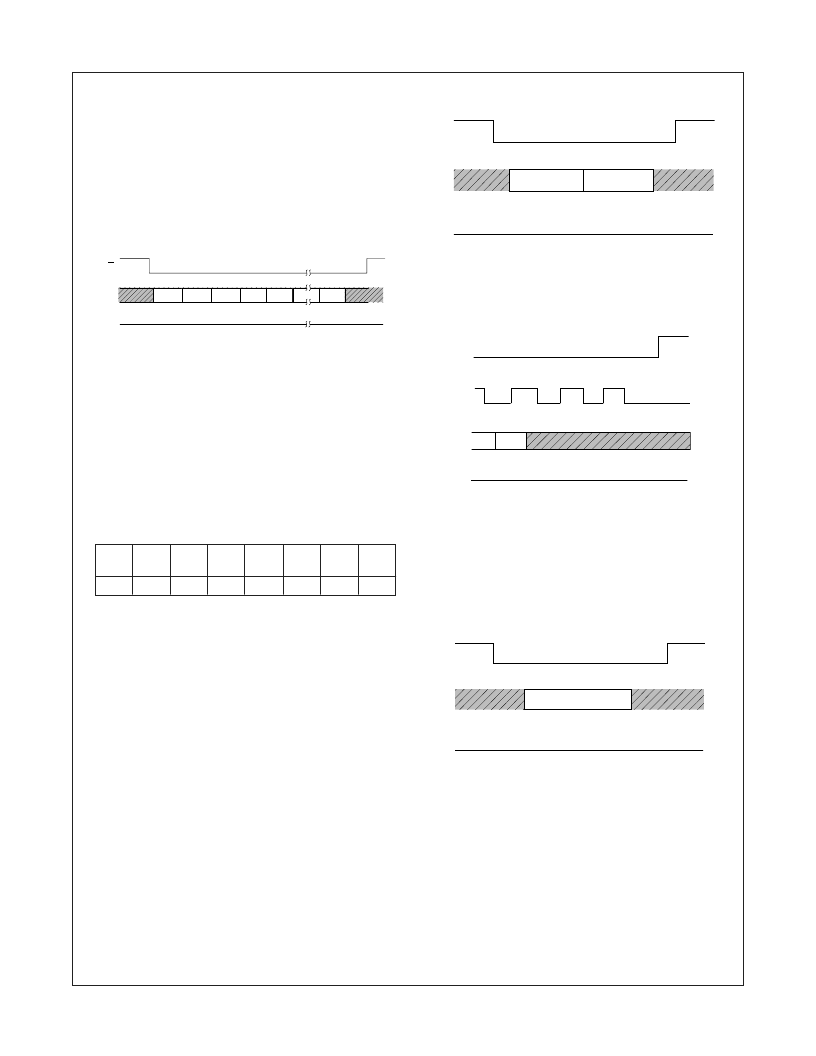

FIGURE 11. Page Write

CS

SI

SO

Write

Opcode

High Addr

Byte

Low Addr

Byte

Data

(1)

Data

(2)

Data

(16)

High Z

/CS

SI

SO

WRSR

Op-Code

SR Data

xxxxBP1BP0xx

FIGURE 12. Write Status Register

BP0

SCK

SI

SO

/CS

/CS

SI

SO

INVALID CODE

At the completion of a write cycle the EEPROM is automatically

returned to the write disabled state. Note that if the EEPROM is not

write enabled (WEN=0) before issuing the WRITE instruction, the

EEPROM will ignore the WRITE instruction and return to the

standby state when /CS is brought high.

WRITE STATUS REGISTER (WRSR):

The Write Status Register (WRSR) instruction provides write

access to the status register. This instruction is used to set Block

Write protection to a portion of the array as defined under Table

4. During a WRSR instruction only Bit3 (BP1) and Bit2 (BP0) can

be written with valid information while other bits are ignored.

Following is the format of WRSR data:

Status Register Write Data

Bit

7

X

Bit

6

X

Bit

5

X

Bit

4

X

Bit

3

BP1

Bit

2

BP0

Bit

1

X

Bit

0

X

X = Don

’

t Care

Note that the first four bits are don

’

t care bits followed by BP1 and

BP0 and two more don

’

t care bits.

WRSR instruction is enabled only when /WP pin is held high and

the EEPROM is write enabled previously (via WREN instruction).

WRSR command requires the following sequence. The /CS pin is

pulled low to select the EEPROM and then the WRSR opcode is

transmitted on the SI pin followed by the data to be programmed.

See Figure 12.

Programming will start after the /CS pin is forced back to a high

level. As in the WRITE instruction the LOW to HIGH transition of

the /CS pin must occur during the SCK low time immediately after

clocking in the last don

’

t care bit. See Figure 13.

FIGURE 13. Start WRSR Condition

At the completion of this instruction the EEPROM is automatically

returned to write disabled state.

INVALID OPCODE

If an invalid code is received, then no data is shifted into the

EEPROM, and the SO data output pin remains high impedance

state until a new /CS falling edge reinitializes the serial communi-

cation. See Figure14.

FIGURE 14. Invalid Op-Code

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FM25C160ULN | SERIAL EEPROM|2KX8|CMOS|DIP|8PIN|PLASTIC |

| FM25C160ULVN | SERIAL EEPROM|2KX8|CMOS|DIP|8PIN|PLASTIC |

| FM25C160ULZEN | SERIAL EEPROM|2KX8|CMOS|DIP|8PIN|PLASTIC |

| FM25C160ULZN | SERIAL EEPROM|2KX8|CMOS|DIP|8PIN|PLASTIC |

| FM25C160ULZVM8 | SERIAL EEPROM|2KX8|CMOS|SOP|8PIN|PLASTIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FM25C160ULM8 | 功能描述:電可擦除可編程只讀存儲(chǔ)器 DIP-8 RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| FM25C160ULM8X | 功能描述:電可擦除可編程只讀存儲(chǔ)器 DIP-8 RoHS:否 制造商:Atmel 存儲(chǔ)容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時(shí)鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| FM25C160ULN | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:SERIAL EEPROM|2KX8|CMOS|DIP|8PIN|PLASTIC |

| FM25C160ULVM8 | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| FM25C160ULVN | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:SERIAL EEPROM|2KX8|CMOS|DIP|8PIN|PLASTIC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。