- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄97930 > EPM3032ALC44-4 Eval Board for ISL6118 2.5V to 5V Dual Power Supply Controller with 0.6A Integrated Current Regulation and Timed Delay to Latch-off PDF資料下載

參數(shù)資料

| 型號(hào): | EPM3032ALC44-4 |

| 英文描述: | Eval Board for ISL6118 2.5V to 5V Dual Power Supply Controller with 0.6A Integrated Current Regulation and Timed Delay to Latch-off |

| 文件頁(yè)數(shù): | 8/53頁(yè) |

| 文件大?。?/td> | 839K |

| 代理商: | EPM3032ALC44-4 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)當(dāng)前第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)

16

Altera Corporation

MAX 3000A Programmable Logic Device Family Data Sheet

Programmable

Speed/Power

Control

MAX 3000A devices offer a power-saving mode that supports low-power

operation across user-defined signal paths or the entire device. This

feature allows total power dissipation to be reduced by 50% or more

because most logic applications require only a small fraction of all gates to

operate at maximum frequency.

The designer can program each individual macrocell in a MAX 3000A

device for either high-speed or low-power operation. As a result, speed-

critical paths in the design can run at high speed, while the remaining

paths can operate at reduced power. Macrocells that run at low power

incur a nominal timing delay adder (tLPA) for the tLAD, tLAC, tIC, tACL, tEN,

tCPPW and tSEXP parameters.

Output

Conguration

MAX 3000A device outputs can be programmed to meet a variety of

system-level requirements.

MultiVolt I/O Interface

The MAX 3000A device architecture supports the MultiVolt I/O interface

feature, which allows MAX 3000A devices to connect to systems with

differing supply voltages. MAX 3000A devices in all packages can be set

for 2.5-V, 3.3-V, or 5.0-V I/O pin operation. These devices have one set of

VCC pins for internal operation and input buffers (VCCINT), and another

set for I/O output drivers (VCCIO).

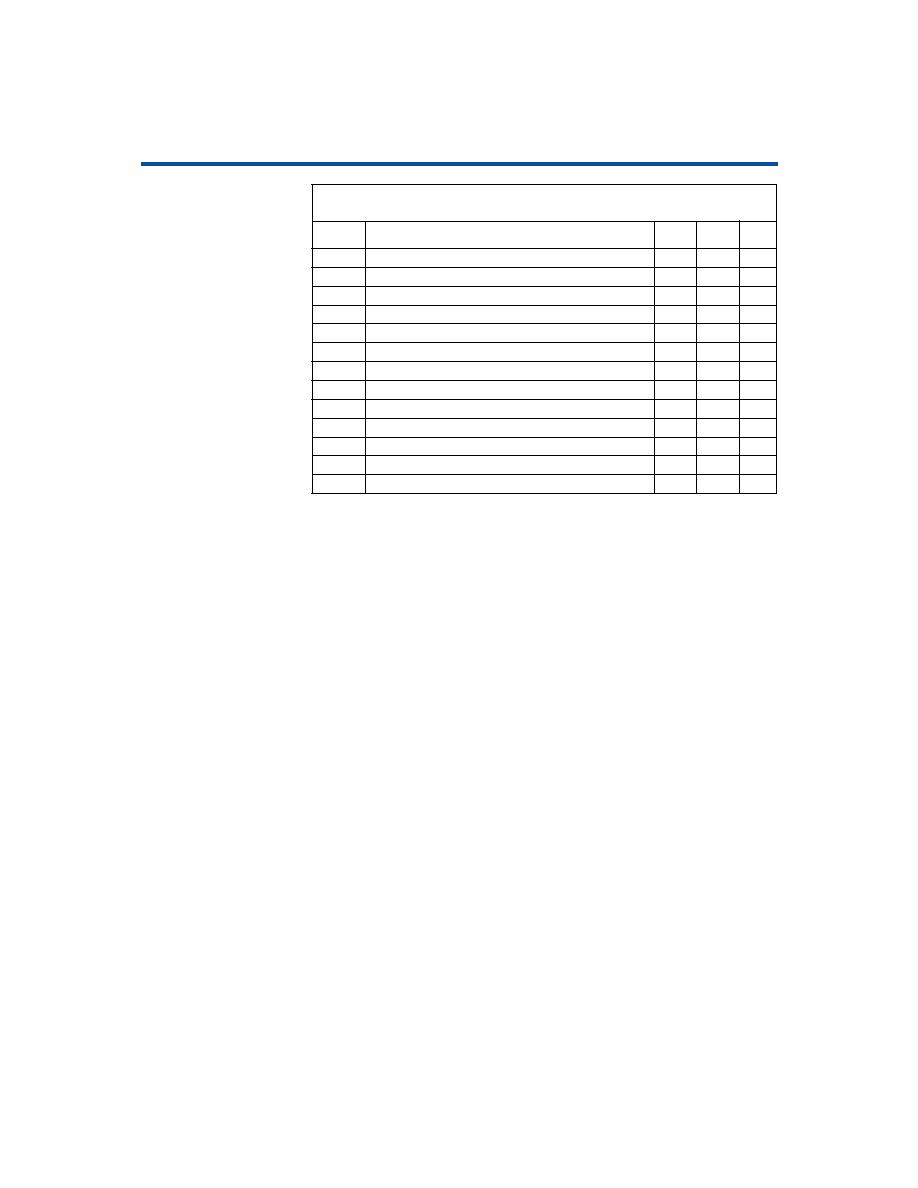

Table 7. JTAG Timing Parameters & Values for MAX 3000A Devices

Symbol

Parameter

Min

Max

Unit

tJCP

TCK

clock period

100

ns

tJCH

TCK

clock high time

50

ns

tJCL

TCK

clock low time

50

ns

tJPSU

JTAG port setup time

20

ns

tJPH

JTAG port hold time

45

ns

tJPCO

JTAG port clock to output

25

ns

tJPZX

JTAG port high impedance to valid output

25

ns

tJPXZ

JTAG port valid output to high impedance

25

ns

tJSSU

Capture register setup time

20

ns

tJSH

Capture register hold time

45

ns

tJSCO

Update register clock to output

25

ns

tJSZX

Update register high impedance to valid output

25

ns

tJSXZ

Update register valid output to high impedance

25

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EPM3032ALC44-7 | Electrically-Erasable Complex PLD |

| EPM3032ATC44-10 | |

| EPM3064ATC44-4 | |

| EPM3064ATC44-7 | Electrically-Erasable Complex PLD |

| EPM3128ATC100-10 | |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EPM3032ALC44-4N | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 CPLD - MAX 3000A 32 Macro 34 IOs RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類(lèi)型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| EPM3032ALC44-7 | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 CPLD - MAX 3000A 32 Macro 34 IOs RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類(lèi)型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| EPM3032ALC44-7N | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 CPLD - MAX 3000A 32 Macro 34 IOs RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類(lèi)型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| EPM3032ALI44-10 | 功能描述:IC MAX 3000A CPLD 32 44-PLCC RoHS:否 類(lèi)別:集成電路 (IC) >> 嵌入式 - CPLD(復(fù)雜可編程邏輯器件) 系列:MAX® 3000A 標(biāo)準(zhǔn)包裝:24 系列:CoolRunner II 可編程類(lèi)型:系統(tǒng)內(nèi)可編程 最大延遲時(shí)間 tpd(1):7.1ns 電壓電源 - 內(nèi)部:1.7 V ~ 1.9 V 邏輯元件/邏輯塊數(shù)目:24 宏單元數(shù):384 門(mén)數(shù):9000 輸入/輸出數(shù):173 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:208-BFQFP 供應(yīng)商設(shè)備封裝:208-PQFP(28x28) 包裝:托盤(pán) |

| EPM3032ALI44-10N | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 CPLD - MAX 3000A 32 Macro 34 IOs RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類(lèi)型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。