- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄299032 > EPF6024AQI208-3 (ALTERA CORP) LOADABLE PLD, PQFP208 PDF資料下載

參數(shù)資料

| 型號: | EPF6024AQI208-3 |

| 廠商: | ALTERA CORP |

| 元件分類: | PLD |

| 英文描述: | LOADABLE PLD, PQFP208 |

| 封裝: | PLASTIC, QFP-208 |

| 文件頁數(shù): | 16/57頁 |

| 文件大小: | 508K |

| 代理商: | EPF6024AQI208-3 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁

Altera Corporation

23

FLEX 6000 Programmable Logic Device Family Data Sheet

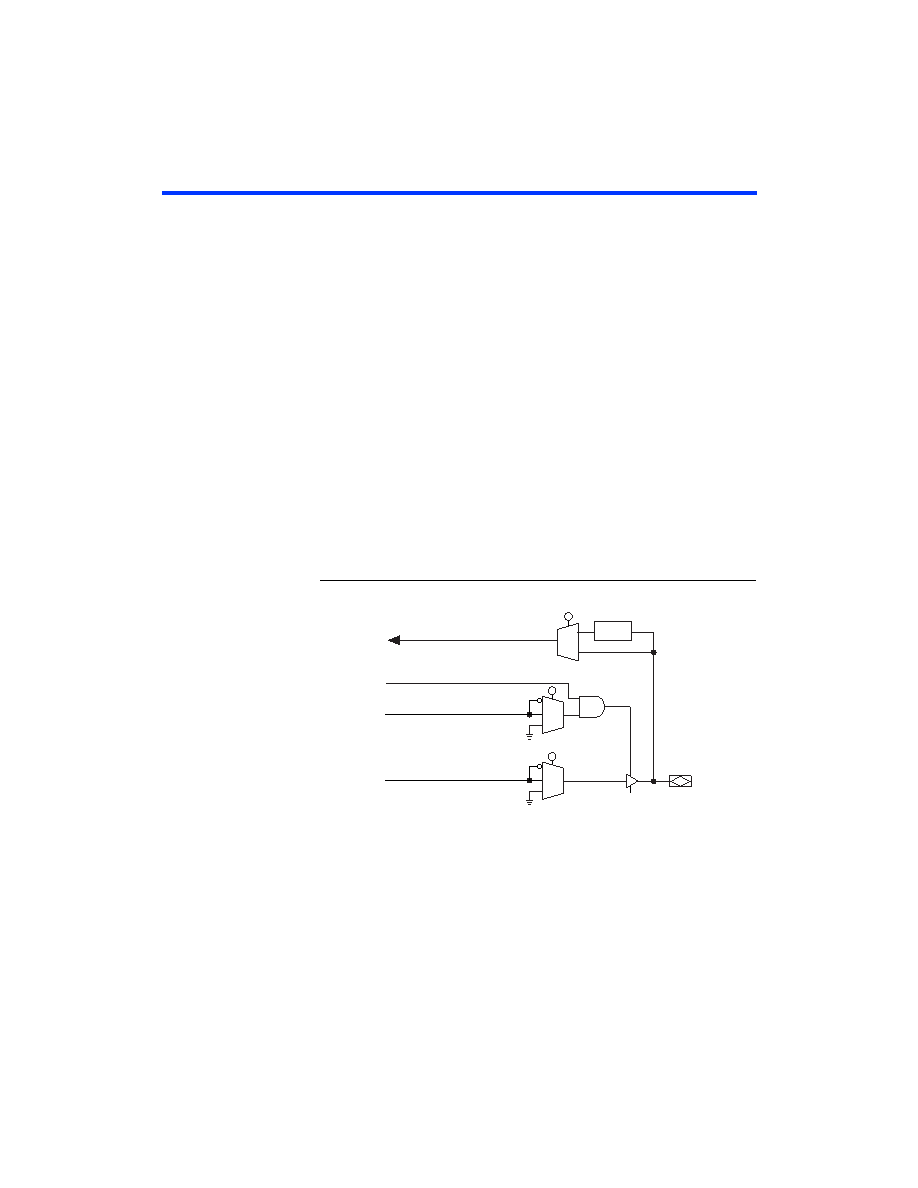

I/O Elements

An IOE contains a bidirectional I/O buffer and a tri-state buffer. IOEs can

be used as input, output, or bidirectional pins. An IOE receives its data

signals from the adjacent local interconnect, which can be driven by a row

or column interconnect (allowing any LE in the device to drive the IOE) or

by an adjacent LE (allowing fast clock-to-output delays). A FastFLEXTM

I/O pin is a row or column output pin that receives its data signals from

the adjacent local interconnect driven by an adjacent LE. The IOE receives

its output enable signal through the same path, allowing individual

output enables for every pin and permitting emulation of open-drain

buffers. The Altera Compiler uses programmable inversion to invert the

data or output enable signals automatically where appropriate. Open-

drain emulation is provided by driving the data input low and toggling

the OE of each IOE. This emulation is possible because there is one OE per

pin.

A chip-wide output enable feature allows the designer to disable all pins

of the device by asserting one pin (DEV_OE). This feature is useful during

board debugging or testing.

Figure 12 shows the IOE block diagram.

Figure 12. IOE Block Diagram

From LAB Local Interconnect

Slew-Rate

Control

From LAB Local Interconnect

To Row or Column Interconnect

Chip-Wide Output Enable

Delay

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EPF6024AQC240-1 | LOADABLE PLD, PQFP240 |

| EPF6024AQC240-2 | LOADABLE PLD, PQFP240 |

| EPF6024AQC240-3 | LOADABLE PLD, PQFP240 |

| EPF6024AFC256-1 | LOADABLE PLD, PBGA256 |

| EPF6024AFC256-2 | LOADABLE PLD, PBGA256 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EPF6024ATC100-2 | 制造商:ALTERA 制造商全稱:Altera Corporation 功能描述:Programmable Logic Device Family |

| EPF6024ATC144-1 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Flex 6000 196 LABs 117 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EPF6024ATC144-1N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Flex 6000 196 LABs 117 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EPF6024ATC144-2 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Flex 6000 196 LABs 117 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EPF6024ATC144-2N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Flex 6000 196 LABs 117 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。