- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄299032 > EPF6024AFC256-1 (ALTERA CORP) LOADABLE PLD, PBGA256 PDF資料下載

參數(shù)資料

| 型號: | EPF6024AFC256-1 |

| 廠商: | ALTERA CORP |

| 元件分類: | PLD |

| 英文描述: | LOADABLE PLD, PBGA256 |

| 封裝: | FINE LINE, BGA-256 |

| 文件頁數(shù): | 24/57頁 |

| 文件大?。?/td> | 508K |

| 代理商: | EPF6024AFC256-1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當(dāng)前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁

30

Altera Corporation

FLEX 6000 Programmable Logic Device Family Data Sheet

Generic Testing

Each FLEX 6000 device is functionally tested. Complete testing of each

configurable SRAM bit and all logic functionality ensures 100%

configuration yield. AC test measurements for FLEX 6000 devices are

made under conditions equivalent to those shown in Figure 17. Multiple

test patterns can be used to configure devices during all stages of the

production flow.

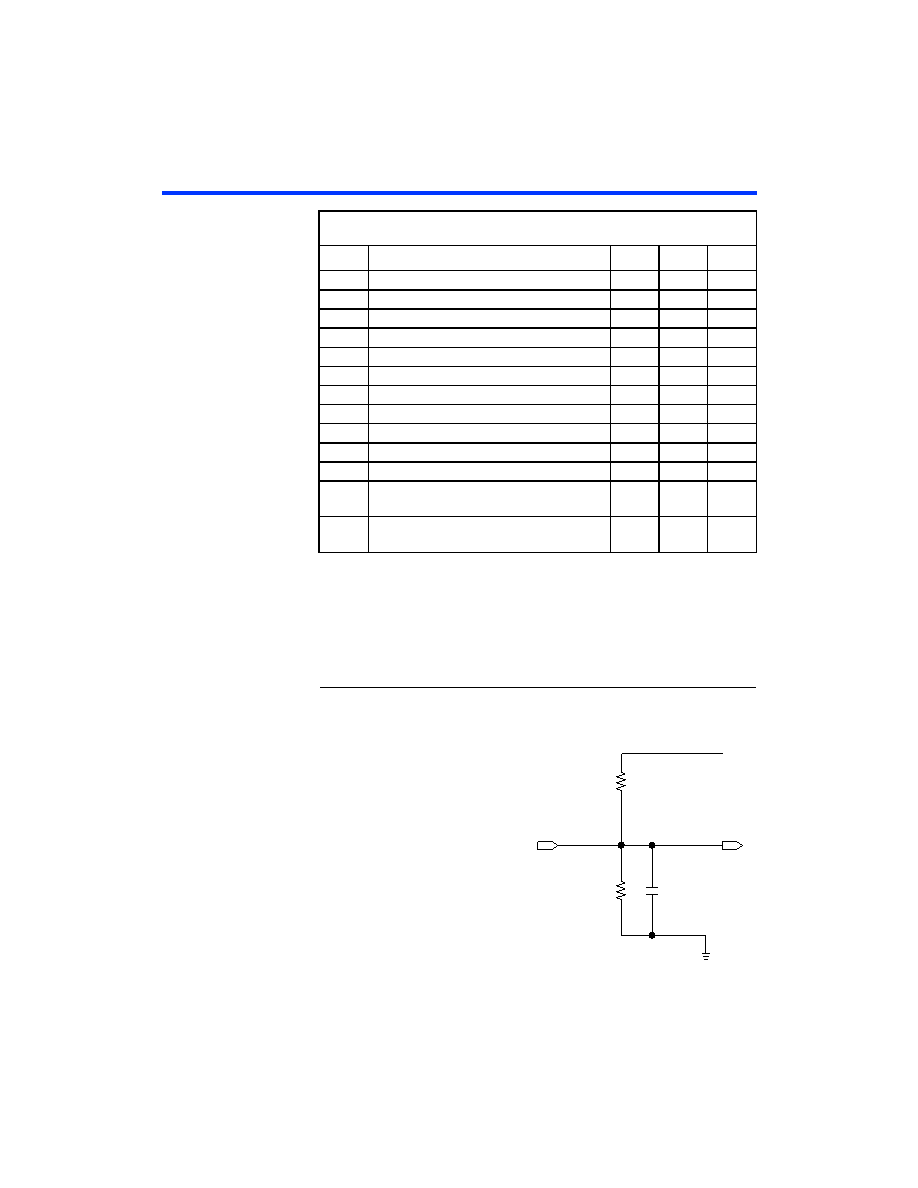

Figure 17. AC Test Conditions

Table 10. JTAG Timing Parameters & Values

Symbol

Parameter

Min

Max

Unit

tJCP

TCK

clock period

100

ns

tJCH

TCK

clock high time

50

ns

tJCL

TCK

clock low time

50

ns

tJPSU

JTAG port setup time

20

ns

tJPH

JTAG port hold time

45

ns

tJPCO

JTAG port clock-to-output

25

ns

tJPZX

JTAG port high impedance to valid output

25

ns

tJPXZ

JTAG port valid output to high impedance

25

ns

tJSSU

Capture register setup time

20

ns

tJSH

Capture register hold time

45

ns

tJSCO

Update register clock-to-output

35

ns

tJSZX

Update register high impedance to valid

output

35

ns

tJSXZ

Update register valid output to high

impedance

35

ns

VCC

To Test

System

C1 (includes

JIG capacitance)

Device input

rise and fall

times < 3 ns

464

(703

)

Device

Output

(8.06 k

)

[521

]

[481

]

250

Power supply transients can affect

AC measurements. Simultaneous

transitions of multiple outputs

should be avoided for accurate

measurement. Threshold tests must

not be performed under AC conditions.

Large-amplitude, fast-ground-current

transients normally occur as the

device outputs discharge the load

capacitances. When these transients

flow through the parasitic

inductance between the device

ground pin and the test system ground,

significant reductions in observable

noise immunity can result. Numbers

without parentheses are for 5.0-V

devices or outputs. Numbers in

parentheses are for 3.3-V devices or

outputs. Numbers in brackets are for

2.5-V devices or outputs.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EPF6024AFC256-2 | LOADABLE PLD, PBGA256 |

| EPF6024AFI256-2 | LOADABLE PLD, PBGA256 |

| EPF6024AFC256-3 | LOADABLE PLD, PBGA256 |

| EPL2010-102MLB | Power inductor, shielded, 20% tol, SMT, RoHS |

| EPL2010-102MLC | Power inductor, shielded, 20% tol, SMT, RoHS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EPF6024AFC256-2 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Flex 6000 196 LABs 219 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EPF6024AFC256-2AA | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| EPF6024AFC256-3 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Flex 6000 196 LABs 219 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EPF6024AFI256-2 | 功能描述:IC FLEX 6000 FPGA 24K 256-FBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:FLEX 6000 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標準包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計:3200 輸入/輸出數(shù):80 門數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應(yīng)商設(shè)備封裝:120-CPGA(34.55x34.55) |

| EPF6024AQC208-1 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Flex 6000 196 LABs 171 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。