- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄22017 > EPF6016QC208-2N (Altera)IC FLEX 6000 FPGA 16K 208-PQFP PDF資料下載

參數(shù)資料

| 型號: | EPF6016QC208-2N |

| 廠商: | Altera |

| 文件頁數(shù): | 35/52頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FLEX 6000 FPGA 16K 208-PQFP |

| 產(chǎn)品培訓(xùn)模塊: | Three Reasons to Use FPGA's in Industrial Designs |

| 標(biāo)準(zhǔn)包裝: | 144 |

| 系列: | FLEX 6000 |

| LAB/CLB數(shù): | 132 |

| 邏輯元件/單元數(shù): | 1320 |

| 輸入/輸出數(shù): | 171 |

| 門數(shù): | 16000 |

| 電源電壓: | 4.75 V ~ 5.25 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 208-BFQFP |

| 供應(yīng)商設(shè)備封裝: | 208-PQFP(28x28) |

| 其它名稱: | 544-1953 EPF6016QC208-2N-ND |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁當(dāng)前第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

40

Altera Corporation

FLEX 6000 Programmable Logic Device Family Data Sheet

Notes to tables:

(1)

Microparameters are timing delays contributed by individual architectural elements and cannot be measured

explicitly.

(2)

Operating conditions:

VCCIO = 5.0 V ±5% for commercial use in 5.0-V FLEX 6000 devices.

VCCIO = 5.0 V ±10% for industrial use in 5.0-V FLEX 6000 devices.

VCCIO = 3.3 V ±10% for commercial or industrial use in 3.3-V FLEX 6000 devices.

(3)

Operating conditions:

VCCIO = 3.3 V ±10% for commercial or industrial use in 5.0-V FLEX 6000 devices.

VCCIO = 2.5 V ±0.2 V for commercial or industrial use in 3.3-V FLEX 6000 devices.

(4)

Operating conditions:

VCCIO = 2.5 V, 3.3 V, or 5.0 V.

(5)

These parameters are worst-case values for typical applications. Post-compilation timing simulation and timing

analysis are required to determine actual worst-case performance.

(6)

This timing parameter shows the delay of a register-to-register test pattern and is used to determine speed grades.

There are 12 LEs, including source and destination registers. The row and column interconnects between the

registers vary in length.

(7)

This timing parameter is shown for reference and is specified by characterization.

(8)

This timing parameter is specified by characterization.

EPF6016A devices.

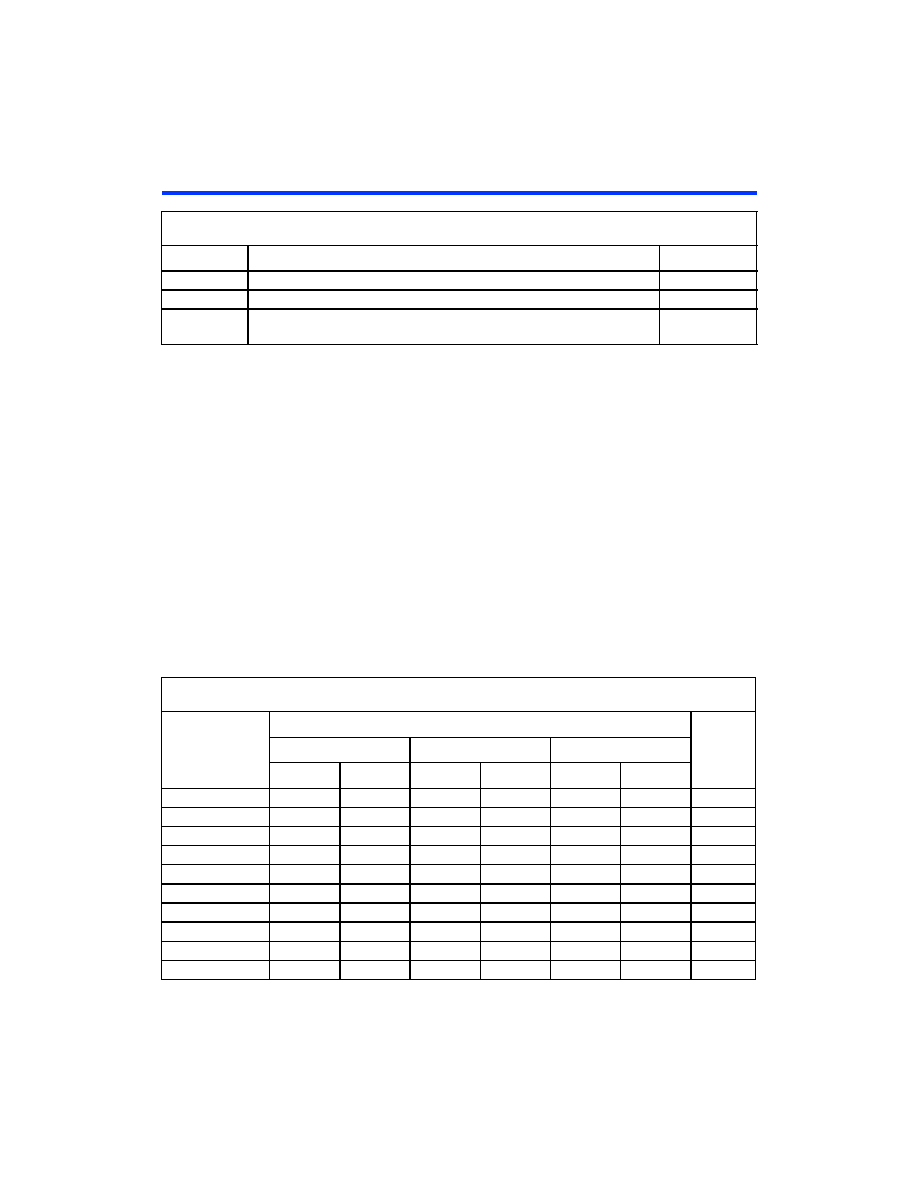

Table 23. External Timing Parameters

Symbol

Parameter

Conditions

tINSU

Setup time with global clock at LE register

tINH

Hold time with global clock at LE register

tOUTCO

Clock-to-output delay with global clock with LE register using FastFLEX I/O

pin

Table 24. LE Timing Microparameters for EPF6010A & EPF6016A Devices (Part 1 of 2)

Parameter

Speed Grade

Unit

-1

-2

-3

Min

Max

Min

Max

Min

Max

tREG_TO_REG

1.2

1.3

1.7

ns

tCASC_TO_REG

0.9

1.0

1.2

ns

tCARRY_TO_REG

0.9

1.0

1.2

ns

tDATA_TO_REG

1.1

1.2

1.5

ns

tCASC_TO_OUT

1.3

1.4

1.8

ns

tCARRY_TO_OUT

1.6

1.8

2.3

ns

tDATA_TO_OUT

1.7

2.0

2.5

ns

tREG_TO_OUT

0.4

0.5

ns

tSU

0.9

1.0

1.3

ns

tH

1.4

1.7

2.1

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RS1D | DIODE GPP FAST 1A 200V SMA |

| D09S24B6GI00LF | CONN DSUB RCPT 9 POS T/H GOLD |

| D09P90C6PV00LF | DSUB VERT PRESS-FIT 9 PIN |

| RSM40DTKT | CONN EDGECARD 80POS DIP .156 SLD |

| PCA9635PW/Q900,118 | IC LED DRIVER RGBA 28-TSSOP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EPF6016QC2083 | 制造商:ALTERA 功能描述:* |

| EPF6016QC208-3 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Flex 6000 132 LABs 171 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EPF6016QC208-3N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Flex 6000 132 LABs 171 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EPF6016QC240-2 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Flex 6000 132 LABs 199 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EPF6016QC240-2N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Flex 6000 132 LABs 199 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。