- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄97926 > EPF10K100BFC256-3DX ASIC PDF資料下載

參數(shù)資料

| 型號: | EPF10K100BFC256-3DX |

| 英文描述: | ASIC |

| 中文描述: | 專用集成電路 |

| 文件頁數(shù): | 76/120頁 |

| 文件大?。?/td> | 1901K |

| 代理商: | EPF10K100BFC256-3DX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁當(dāng)前第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁

Altera Corporation

59

FLEX 10KE Embedded Programmable Logic Family Data Sheet

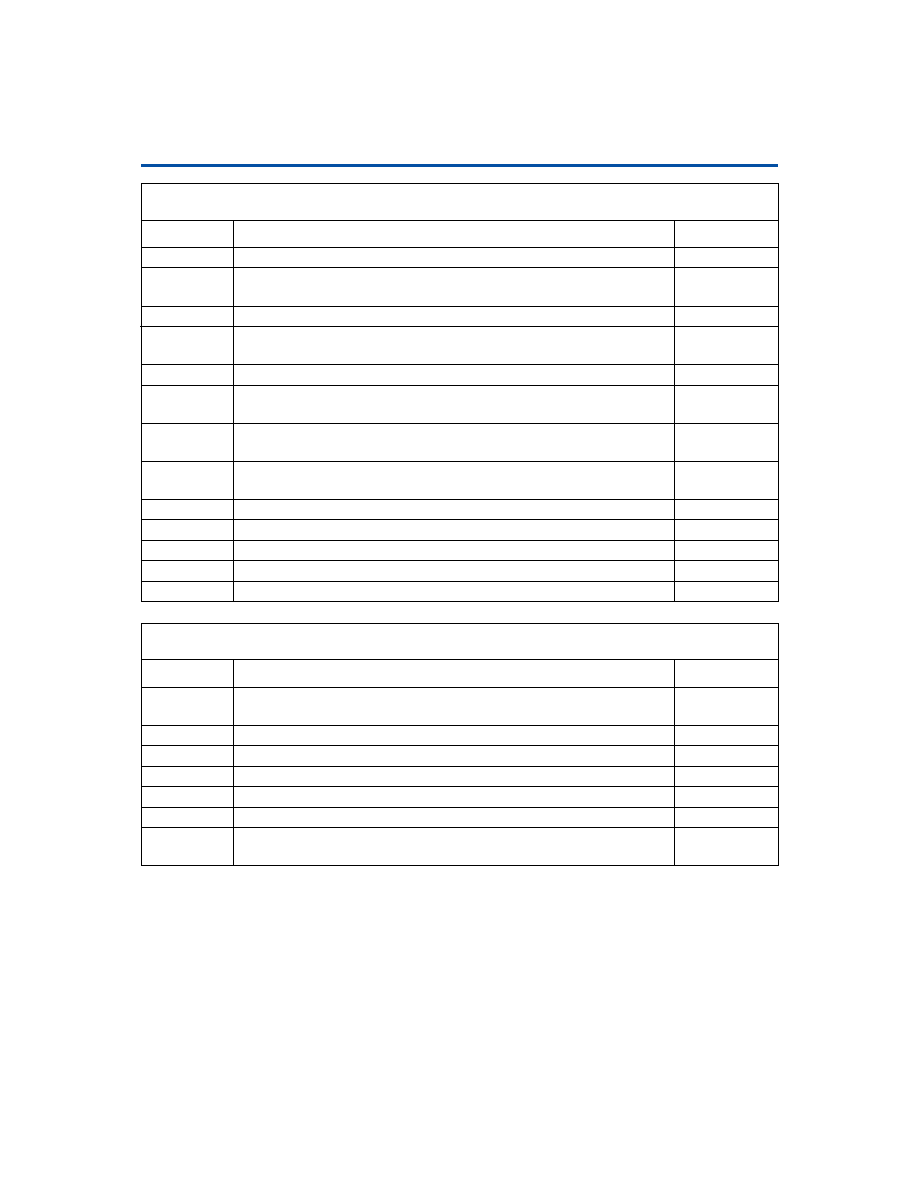

Table 28. Interconnect Timing Microparameters

Symbol

Parameter

Conditions

tSAMELAB

Routing delay for an LE driving another LE in the same LAB

tSAMEROW

Routing delay for a row IOE, LE, or EAB driving a row IOE, LE, or EAB in the

same row

tSAMECOLUMN

Routing delay for an LE driving an IOE in the same column

tDIFFROW

Routing delay for a column IOE, LE, or EAB driving an LE or EAB in a

different row

tTWOROWS

Routing delay for a row IOE or EAB driving an LE or EAB in a different row

tLEPERIPH

Routing delay for an LE driving a control signal of an IOE via the peripheral

control bus

tLABCARRY

Routing delay for the carry-out signal of an LE driving the carry-in signal of

a different LE in a different LAB

tLABCASC

Routing delay for the cascade-out signal of an LE driving the cascade-in

signal of a different LE in a different LAB

tDIN2IOE

Delay from dedicated input pin to IOE control input

tDIN2LE

Delay from dedicated input pin to LE or EAB control input

tDCLK2IOE

Delay from dedicated clock pin to IOE clock

tDCLK2LE

Delay from dedicated clock pin to LE or EAB clock

tDIN2DATA

Delay from dedicated input or clock to LE or EAB data

Table 29. External Timing Parameters

Symbol

Parameter

Conditions

tDRR

Register-to-register delay via four LEs, three row interconnects, and

four local interconnects

tINSU

Setup time with global clock at IOE register

tINH

Hold time with global clock at IOE register

tOUTCO

Clock-to-output delay with global clock at IOE register

tPCISU

Setup time with global clock for registers used in PCI designs

tPCIH

Hold time with global clock for registers used in PCI designs

tPCICO

Clock-to-output delay with global clock for registers used in PCI

designs

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EPF10K100BFI256-1DX | ASIC |

| EPF10K100BFI256-2DX | ASIC |

| EPF10K100BFI256-3DX | ASIC |

| EPF10K100BQC208-1DX | ASIC |

| EPF10K100EBC356-1 | Field Programmable Gate Array (FPGA) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EPF10K100BFI256-1DX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

| EPF10K100BFI256-2DX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

| EPF10K100BFI256-3DX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

| EPF10K100BQC208-1 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| EPF10K100BQC208-1DX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ASIC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。