- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4181 > EP2AGX190EF29I3 (Altera)IC ARRIA II GX FPGA 190K 780FBGA PDF資料下載

參數(shù)資料

| 型號: | EP2AGX190EF29I3 |

| 廠商: | Altera |

| 文件頁數(shù): | 35/90頁 |

| 文件大小: | 0K |

| 描述: | IC ARRIA II GX FPGA 190K 780FBGA |

| 標(biāo)準(zhǔn)包裝: | 4 |

| 系列: | Arria II GX |

| LAB/CLB數(shù): | 7612 |

| 邏輯元件/單元數(shù): | 181165 |

| RAM 位總計: | 10177536 |

| 輸入/輸出數(shù): | 372 |

| 電源電壓: | 0.87 V ~ 0.93 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 780-BBGA |

| 供應(yīng)商設(shè)備封裝: | 780-FBGA(29x29) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁當(dāng)前第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁

1–32

Chapter 1: Device Datasheet for Arria II Devices

Switching Characteristics

December 2013

Altera Corporation

-3 dB Bandwidth

PCIe Gen1

2.5 - 3.5

MHz

PCIe Gen2

6 - 8

MHz

(OIF) CEI PHY at

4.976 Gbps

7 - 11

MHz

(OIF) CEI PHY at

6.375 Gbps

5 - 10

MHz

XAUI

2 - 4

MHz

SRIO 1.25 Gbps

3 - 5.5

MHz

SRIO 2.5 Gbps

3 - 5.5

MHz

SRIO 3.125 Gbps

2 - 4

MHz

GIGE

2.5 - 4.5

MHz

SONET OC12

1.5 - 2.5

MHz

SONET OC48

3.5 - 6

MHz

Transceiver-FPGA Fabric Interface

Interface speed

—

25

—

325

25

—

250

MHz

Digital reset pulse width

—

Minimum is two parallel clock cycles

—

Notes to Table 1–35:

(1) The 3x speed grade is the fastest speed grade offered in the following Arria II GZ devices: EP2AGZ225, EP2AGZ300, and EP2AGZ350.

(2) The rise and fall time transition is specified from 20% to 80%.

(3) To calculate the REFCLK rms phase jitter requirement at reference clock frequencies other than 100 MHz, use the following formula:

REFCLK rms phase jitter at f (MHz) = REFCLK rms phase jitter at 100 MHz * 100/f.

(4) The minimum reconfig_clk frequency is 2.5 MHz if the transceiver channel is configured in Transmitter only mode. The minimum

reconfig_clk

frequency is 37.5 MHz if the transceiver channel is configured in Receiver only or Receiver and Transmitter mode.

(5) If your design uses more than one dynamic reconfiguration controller (altgx_reconfig) instances to control the transceiver (altgx)

channels physically located on the same side of the device AND if you use different reconfig_clk sources for these altgx_reconfig

instances, the delta time between any two of these reconfig_clk sources becoming stable must not exceed the maximum specification listed.

(6) The device cannot tolerate prolonged operation at this absolute maximum.

(7) You must use the 1.1-V RX VICM setting if the input serial data standard is LVDS.

(8) The differential eye opening specification at the receiver input pins assumes that Receiver Equalization is disabled. If you enable Receiver

Equalization, the receiver circuitry can tolerate a lower minimum eye opening, depending on the equalization level. Use H-Spice simulation to

derive the minimum eye opening requirement with Receiver Equalization enabled.

(9) The rate matcher supports only up to

± 300 ppm.

(10) Time taken to rx_pll_locked goes high from rx_analogreset de-assertion. Refer to Figure 1–1 on page 1–33.

(11) Time for which the CDR must be kept in lock-to-reference mode after rx_pll_locked goes high and before rx_locktodata is asserted in

manual mode. Refer to Figure 1–1 on page 1–33.

(12) Time taken to recover valid data after the rx_locktodata signal is asserted in manual mode. Refer to Figure 1–1 on page 1–33.

(13) Time taken to recover valid data after the rx_freqlocked signal goes high in automatic mode. Refer to Figure 1–2 on page 1–33.

(14) A GPLL may be required to meet the PMA-FPGA fabric interface timing above certain data rates. For more information, refer to the Transceiver

(15) The Quartus II software automatically selects the appropriate slew rate depending on the configured data rate or functional mode.

(16) To support data rates lower than the minimum specification through oversampling, use the CDR in LTR mode only.

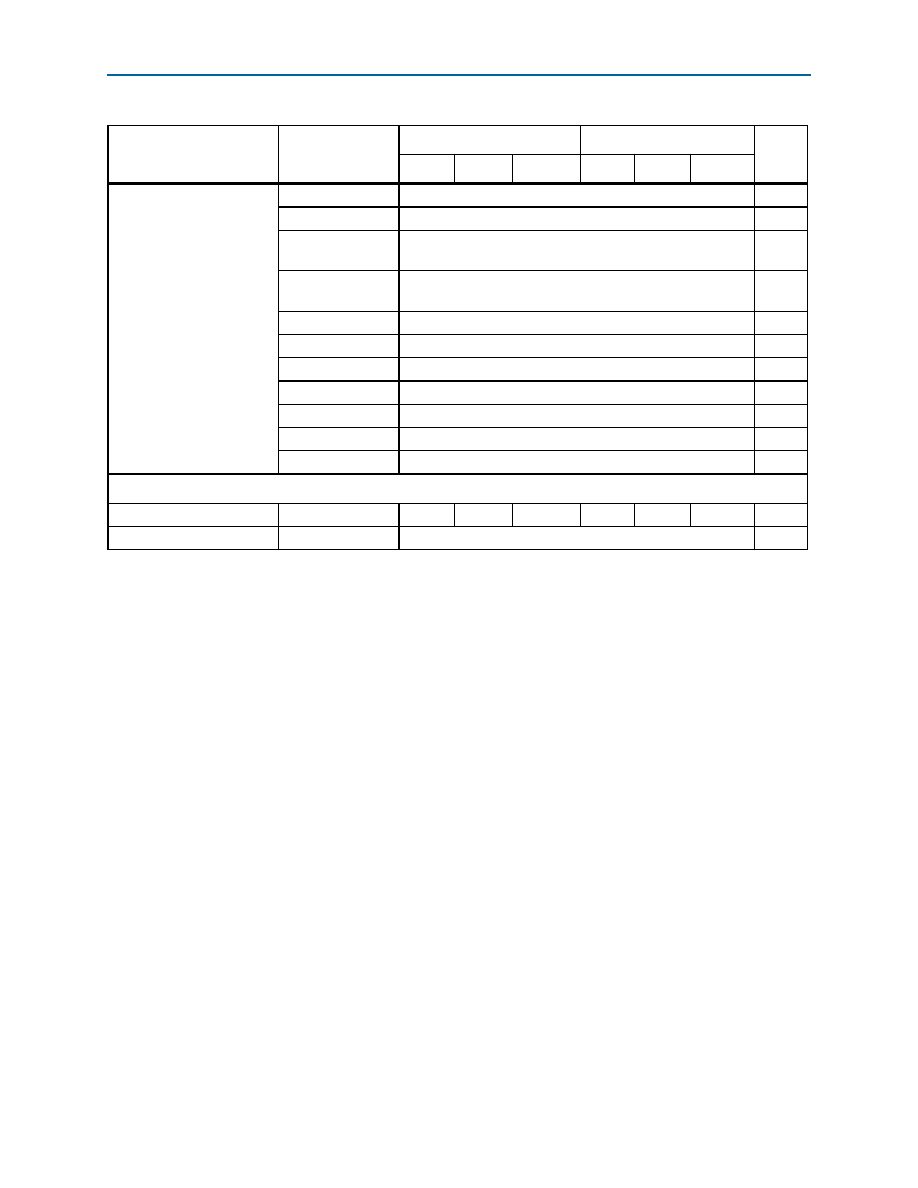

Table 1–35. Transceiver Specifications for Arria II GZ Devices (Part 5 of 5)

Symbol/

Description

Conditions

–C3 and –I3 (1)

–C4 and –I4

Unit

Min

Typ

Max

Min

Typ

Max

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EP2AGX125DF25I3 | IC ARRIA II GX FPGA 125K 572FBGA |

| EP2AGX95EF35I3 | IC ARRIA II GX FPGA 95K 1152FBGA |

| EP2AGX95EF29I3 | IC ARRIA II GX FPGA 95K 780FBGA |

| IDT71V3556S100PFG8 | IC SRAM 4MBIT 100MHZ 100TQFP |

| EP2AGX65DF25I3 | IC ARRIA II GX FPGA 65K 572FBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP2AGX190EF29I3N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Arria II GX 7612 LABs 372 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP2AGX190EF29I5 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Arria II GX 7612 LABs 372 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP2AGX190EF29I5N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Arria II GX 7612 LABs 372 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP2AGX190FF35C4 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Arria II GX 7612 LABs 612 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP2AGX190FF35C4N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Arria II GX 7612 LABs 612 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。