- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄299032 > EP20K400ERI240-3 (ALTERA CORP) LOADABLE PLD, PQFP240 PDF資料下載

參數(shù)資料

| 型號(hào): | EP20K400ERI240-3 |

| 廠商: | ALTERA CORP |

| 元件分類: | PLD |

| 英文描述: | LOADABLE PLD, PQFP240 |

| 封裝: | HEAT SINK, POWER, QFP-240 |

| 文件頁數(shù): | 23/65頁 |

| 文件大小: | 781K |

| 代理商: | EP20K400ERI240-3 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當(dāng)前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁

Altera Corporation

25

Preliminary Information

APEX 20K Programmable Logic Device Family Data Sheet

s

Advanced interconnect structure

–

Four-level hierarchical FastTrack Interconnect structure

providing fast, predictable interconnect delays

–

Dedicated carry chain that implements arithmetic functions such

as fast adders, counters, and comparators (automatically used by

software tools and megafunctions)

–

Dedicated cascade chain that implements high-speed,

high-fan-in logic functions (automatically used by software tools

and megafunctions)

–

Interleaved local interconnect allows one LE to drive 29 other

LEs through the fast local interconnect

s

Advanced packaging options

–

Available in a variety of packages with 144 to 984 pins (see

–

FineLine BGATM packages maximize board space efficiency

–

SameFrameTM pin migration providing migration capability

across device densities and package sizes

s

Advanced software support

–

Software design support and automatic place-and-route

provided by the Altera QuartusTM development system for

Windows-based PCs, Sun SPARCstations, and HP 9000

Series 700/800 workstations

–

Altera MegaCoreTM functions and Altera Megafunction Partners

Program (AMPPSM) megafunctions

–

NativeLinkTM integration with popular synthesis, simulation,

and timing analysis tools

–

Quartus SignalTapTM embedded logic analyzer simplifying

in-system design evaluation by giving access to internal nodes

during device operation

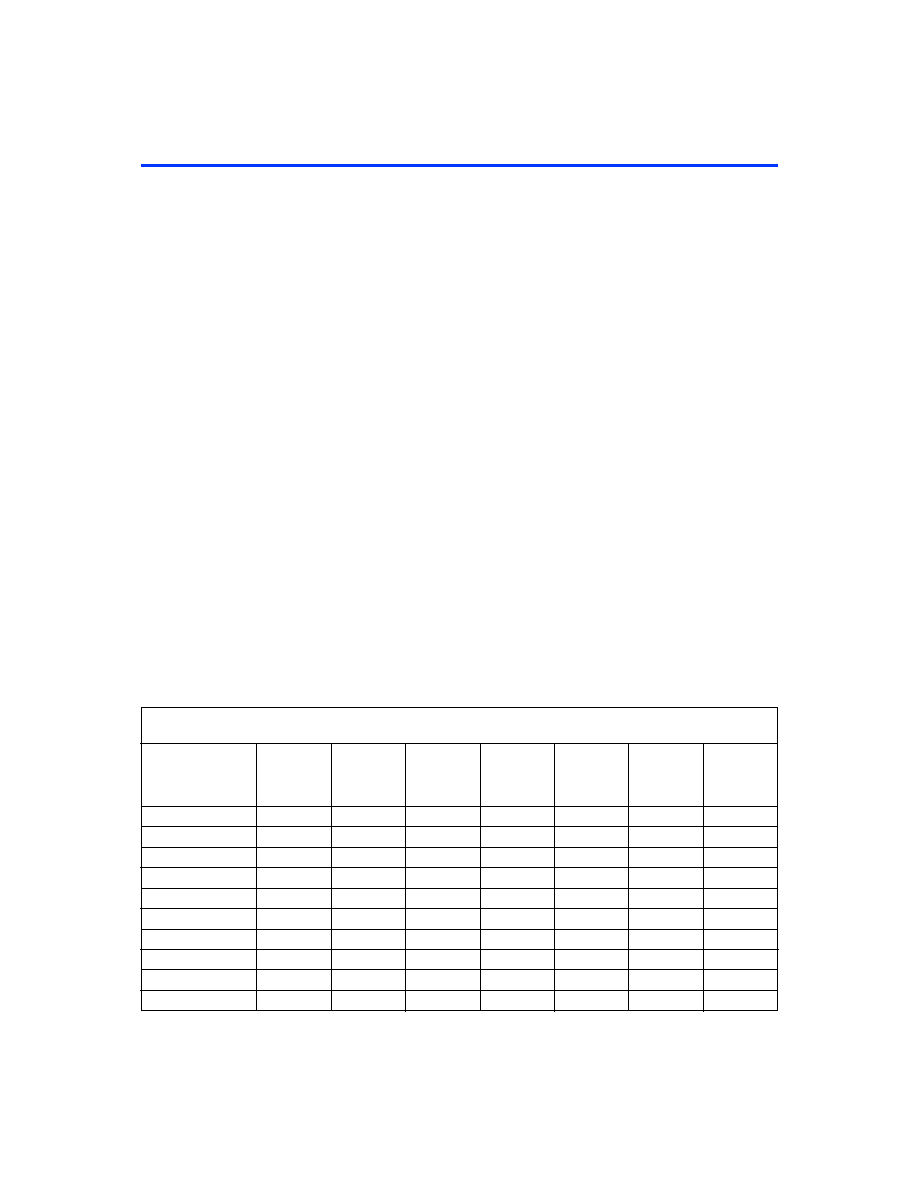

Table 3. APEX 20K QFP, BGA & PGA Package Options & I/O Count

Device

144-Pin

TQFP

208-Pin

PQFP

RQFP

240-Pin

PQFP

RQFP

356-Pin

BGA

652-Pin

BGA

655-Pin

PGA

984-Pin

PGA

EP20K100

101

159

189

252

EP20K100E

92

149

181

v

EP20K160E

84

141

173

v

EP20K200

144

174

v

EP20K200E

134

166

v

EP20K300E

118

150

v

EP20K400

502

EP20K400E

100

132

v

EP20K600E

v

EP20K1000E

v

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EP20K400FC672-3X | LOADABLE PLD, 3.6 ns, PBGA672 |

| EPB5065G | 42 MHz, LOW PASS FILTER |

| EPC1000P | 1-OUTPUT DC-DC REG PWR SUPPLY MODULE |

| EPC1055PE | 1-OUTPUT DC-DC REG PWR SUPPLY MODULE |

| EPC1195G-5 | 1-OUTPUT 0.5 W DC-DC UNREG PWR SUPPLY MODULE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP20K400FC672-1 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 CPLD - APEX 20K 1664 Macros 502 IO RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP20K400FC672-1ES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

| EP20K400FC672-1X | 功能描述:FPGA - 現(xiàn)場可編程門陣列 CPLD - APEX 20K 1664 Macros 502 IO RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP20K400FC672-2 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 CPLD - APEX 20K 1664 Macros 502 IO RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP20K400FC672-2ES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。