- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄97922 > EP20K160EFC484-2ES FPGA PDF資料下載

參數(shù)資料

| 型號: | EP20K160EFC484-2ES |

| 英文描述: | FPGA |

| 中文描述: | FPGA的 |

| 文件頁數(shù): | 82/114頁 |

| 文件大小: | 1623K |

| 代理商: | EP20K160EFC484-2ES |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁當(dāng)前第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁

Altera Corporation

7

APEX 20K Programmable Logic Device Family Data Sheet

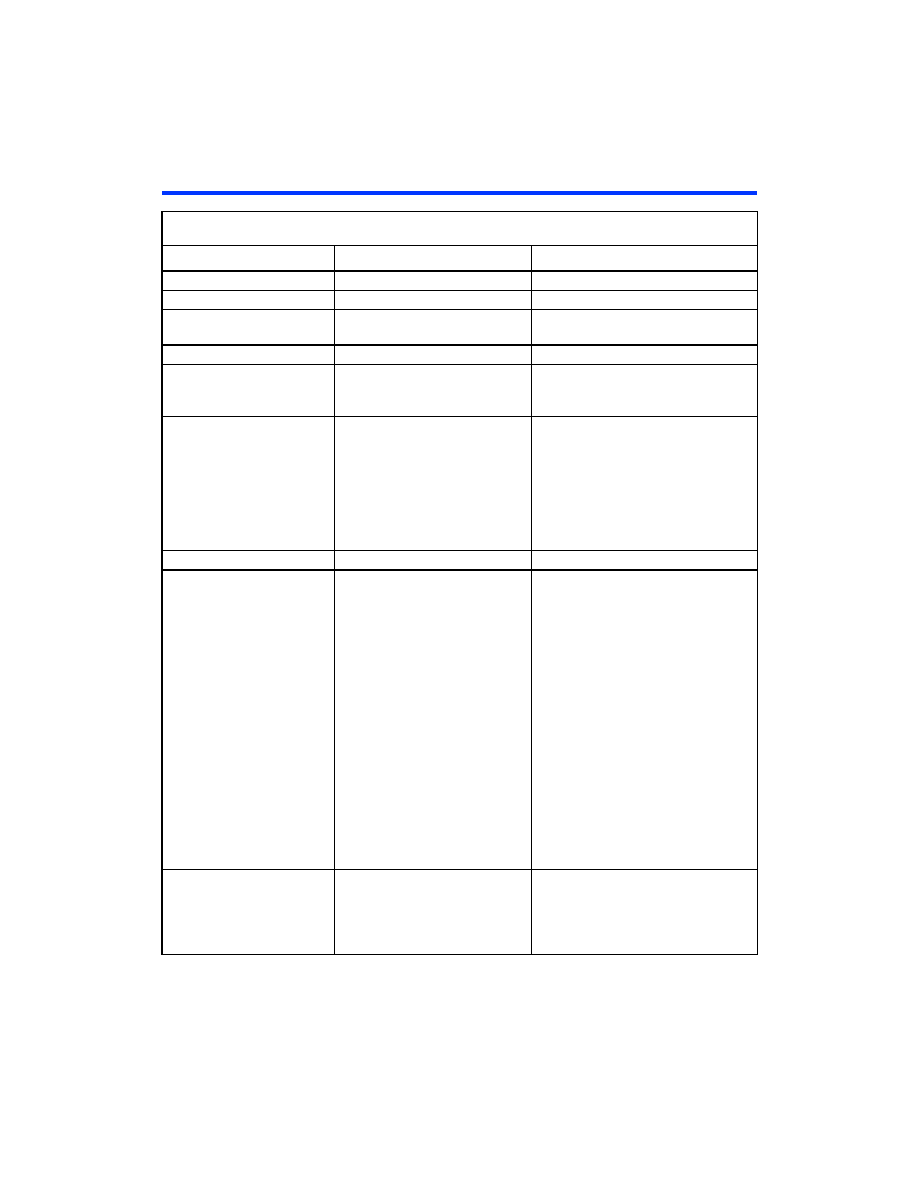

Table 8. Comparison of APEX 20K & APEX 20KE Features

Feature

APEX 20K Devices

APEX 20KE Devices

MultiCore system integration

Full support

SignalTap logic analysis

Full support

32/64-Bit, 33-MHz PCI

Full compliance in -1, -2 speed

grades

Full compliance in -1, -2 speed grades

32/64-Bit, 66-MHz PCI

-

Full compliance in -1 speed grade

MultiVolt I/O

2.5-V or 3.3-V VCCIO

VCCIO selected for device

Certain devices are 5.0-V tolerant

1.8-V, 2.5-V, or 3.3-V VCCIO

VCCIO selected block-by-block

5.0-V tolerant with use of external resistor

ClockLock support

Clock delay reduction

2

× and 4× clock multiplication

Clock delay reduction

m /(n

× v) or m/(n × k) clock multiplication

Drive ClockLock output off-chip

External clock feedback

ClockShift

LVDS support

Up to four PLLs

ClockShift, clock phase adjustment

Dedicated clock and input pins Six

Eight

I/O standard support

2.5-V, 3.3-V, 5.0-V I/O

3.3-V PCI

Low-voltage complementary

metal-oxide semiconductor

(LVCMOS)

Low-voltage transistor-to-transistor

logic (LVTTL)

1.8-V, 2.5-V, 3.3-V, 5.0-V I/O

2.5-V I/O

3.3-V PCI and PCI-X

3.3-V Advanced Graphics Port (AGP)

Center tap terminated (CTT)

GTL+

LVCMOS

LVTTL

True-LVDS and LVPECL data pins

(in EP20K300E and larger devices)

LVDS and LVPECL clock pins (in all

devices)

LVDS and LVPECL data pins up to

156 Mbps (in -1 speed grade devices)

HSTL Class I

PCI-X

SSTL-2 Class I and II

SSTL-3 Class I and II

Memory support

Dual-port RAM

FIFO

RAM

ROM

CAM

Dual-port RAM

FIFO

RAM

ROM

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EP20K160EFC484-3ES | 5V, Byte Alterable E2PROM; Temperature Range: -55°C to 125°C; Package: 32-FlatPack |

| EP20K160EFI484-1ES | FPGA |

| EP20K160EFI484-2ES | 5V, Byte Alterable E2PROM; Temperature Range: 0°C to 70°C; Package: 36-PGA |

| EP20K160EFI484-3ES | 5V, Byte Alterable E2PROM; Temperature Range: -55°C to 125°C; Package: 36-PGA |

| EP20K160EQC208-1ES | FPGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP20K160EFC484-2N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 CPLD - APEX 20K 640 Macro 316 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP20K160EFC484-2X | 功能描述:FPGA - 現(xiàn)場可編程門陣列 CPLD - APEX 20K 640 Macro 316 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP20K160EFC4843 | 制造商:Altera Corporation 功能描述: |

| EP20K160EFC484-3 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 CPLD - APEX 20K 640 Macro 316 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP20K160EFC484-3ES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。