- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄22017 > EP1K50FC484-3N (Altera)IC ACEX 1K FPGA 50K 484-FBGA PDF資料下載

參數(shù)資料

| 型號: | EP1K50FC484-3N |

| 廠商: | Altera |

| 文件頁數(shù): | 42/86頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC ACEX 1K FPGA 50K 484-FBGA |

| 產(chǎn)品培訓(xùn)模塊: | Three Reasons to Use FPGA's in Industrial Designs |

| 標準包裝: | 60 |

| 系列: | ACEX-1K® |

| LAB/CLB數(shù): | 360 |

| 邏輯元件/單元數(shù): | 2880 |

| RAM 位總計: | 40960 |

| 輸入/輸出數(shù): | 249 |

| 門數(shù): | 199000 |

| 電源電壓: | 2.375 V ~ 2.625 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 70°C |

| 封裝/外殼: | 484-BGA |

| 供應(yīng)商設(shè)備封裝: | 484-FBGA(23x23) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁當前第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁

Altera Corporation

47

ACEX 1K Programmable Logic Device Family Data Sheet

D

e

ve

lo

pm

e

n

t

13

To

o

ls

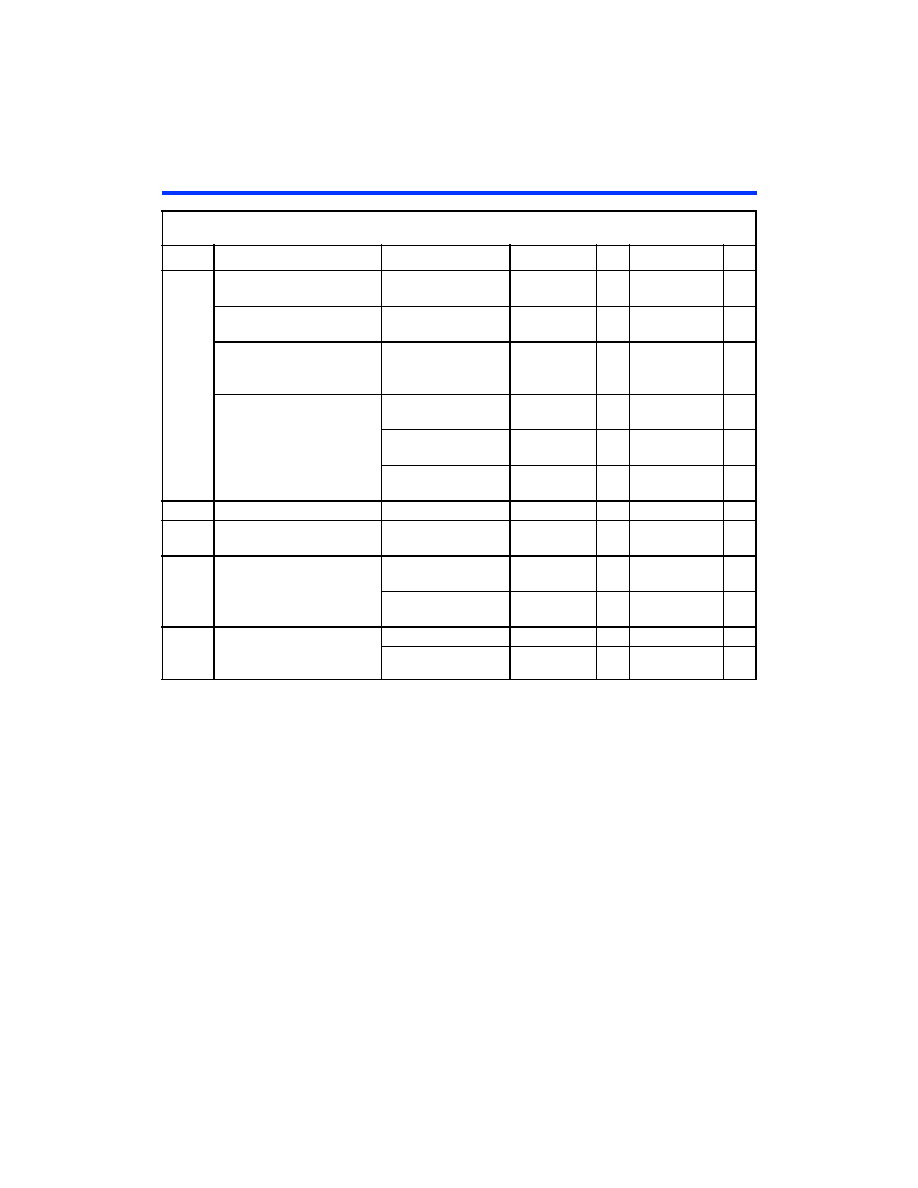

VOL

3.3-V low-level TTL output

voltage

IOL = 12 mA DC,

0.45

V

3.3-V low-level CMOS output

voltage

IOL = 0.1 mA DC,

0.2

V

3.3-V low-level PCI output

voltage

IOL = 1.5 mA DC,

VCCIO = 3.00 to 3.60 V

0.1

× V

CCIO

V

2.5-V low-level output voltage IOL = 0.1 mA DC,

0.2

V

IOL = 1 mA DC,

0.4

V

IOL = 2 mA DC,

0.7

V

II

Input pin leakage current

–10

10

A

IOZ

Tri-stated I/O pin leakage

current

–10

10

A

ICC0

VCC supply current (standby) VI = ground, no load,

no toggling inputs

5mA

VI = ground, no load,

no toggling inputs (12)

10

mA

RCONF

Value of I/O pin pull-up

resistor before and during

configuration

20

50

k

30

80

k

Table 20. ACEX 1K Device DC Operating Conditions (Part 2 of 2)

Notes (6), (7)

Symbol

Parameter

Conditions

Min

Typ

Max

Unit

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADT7485AARMZ-REEL7 | IC TEMP/VOLT DGL SENS SST 10MSOP |

| EP1K50FC484-3 | IC ACEX 1K FPGA 50K 484-FBGA |

| REC3-0509SRW/H/B/M | CONV DC/DC 3W 4.5-9VIN 09VOUT |

| TPSC157M004R0080 | CAP TANT 150UF 4V 20% 2312 |

| ABE35DHFR | CONN CARDEDGE 70POS 1MM SMD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP1K50FI256-1DX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| EP1K50FI256-1F | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| EP1K50FI256-1P | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| EP1K50FI256-1X | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| EP1K50FI256-2 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - ACEX 1K 360 LABs 186 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。