- 您現在的位置:買賣IC網 > PDF目錄362735 > EP1C6Q256C8ES (Altera Corporation) Cyclone FPGA Family Data Sheet PDF資料下載

參數資料

| 型號: | EP1C6Q256C8ES |

| 廠商: | Altera Corporation |

| 英文描述: | Cyclone FPGA Family Data Sheet |

| 中文描述: | 氣旋的FPGA系列數據手冊 |

| 文件頁數: | 25/104頁 |

| 文件大小: | 763K |

| 代理商: | EP1C6Q256C8ES |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁

Altera Corporation

January 2007

2–19

Preliminary

Embedded Memory

In addition to true dual-port memory, the M4K memory blocks support

simple dual-port and single-port RAM. Simple dual-port memory

supports a simultaneous read and write. Single-port memory supports

non-simultaneous reads and writes.

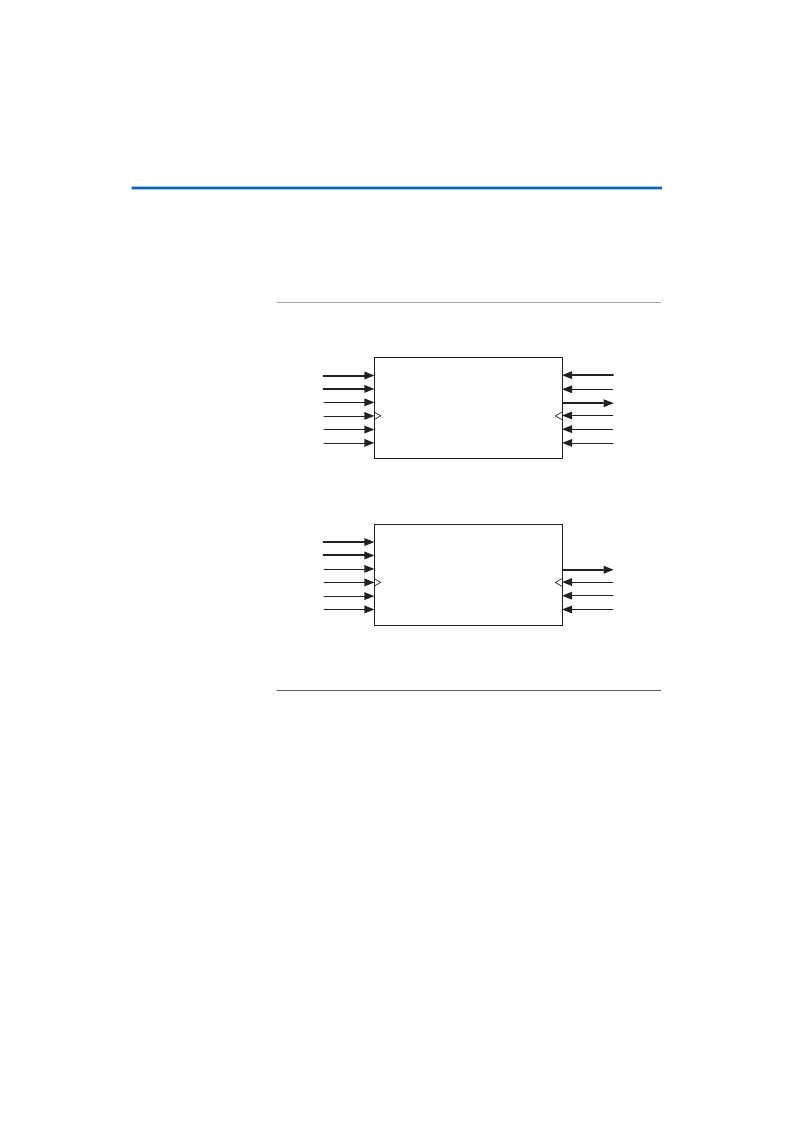

Figure 2–13

shows these different

M4K RAM memory port configurations.

Figure 2–13. Simple Dual-Port & Single-Port Memory Configurations

Note to

Figure 2–13

:

(1)

Two single-port memory blocks can be implemented in a single M4K block as long

as each of the two independent block sizes is equal to or less than half of the M4K

block size.

The memory blocks also enable mixed-width data ports for reading and

writing to the RAM ports in dual-port RAM configuration. For example,

the memory block can be written in

×

1 mode at port A and read out in

×

16

mode from port B.

The Cyclone memory architecture can implement fully synchronous

RAM by registering both the input and output signals to the M4K RAM

block. All M4K memory block inputs are registered, providing

synchronous write cycles. In synchronous operation, the memory block

generates its own self-timed strobe write enable (

wren

) signal derived

from a global clock. In contrast, a circuit using asynchronous RAM must

generate the RAM

wren

signal while ensuring its data and address

signals meet setup and hold time specifications relative to the

wren

data[

wraddress[

wren

inclock

inclocken

inaclr

rdaddress[

rden

q[

outclock

outclocken

outaclr

data[

address[

wren

inclock

inclocken

inaclr

q[

outclock

outclocken

outaclr

Single-Port Memory

(1)

Simple Dual-Port Memory

相關PDF資料 |

PDF描述 |

|---|---|

| EP1C6Q256I6ES | Cyclone FPGA Family Data Sheet |

| EP1C6Q256I7ES | Cyclone FPGA Family Data Sheet |

| EP1C6Q256I8ES | Cyclone FPGA Family Data Sheet |

| EP1C6Q324C6ES | Cyclone FPGA Family Data Sheet |

| EP1C6Q324C7ES | Cyclone FPGA Family Data Sheet |

相關代理商/技術參數 |

參數描述 |

|---|---|

| EP1C6T144C6 | 功能描述:FPGA - 現場可編程門陣列 FPGA - Cyclone I 598 LABs 98 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數量: 邏輯塊數量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP1C6T144C6N | 功能描述:FPGA - 現場可編程門陣列 FPGA - Cyclone I 598 LABs 98 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數量: 邏輯塊數量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP1C6T144C7 | 功能描述:FPGA - 現場可編程門陣列 FPGA - Cyclone I 598 LABs 98 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數量: 邏輯塊數量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP1C6T144C7N | 功能描述:FPGA - 現場可編程門陣列 FPGA - Cyclone I 598 LABs 98 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數量: 邏輯塊數量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP1C6T144C8 | 功能描述:FPGA - 現場可編程門陣列 FPGA - Cyclone I 598 LABs 98 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數量: 邏輯塊數量:943 內嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購,3分鐘左右您將得到回復。