- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362738 > EP1C6F324I7 (Altera Corporation) Cyclone FPGA Family PDF資料下載

參數(shù)資料

| 型號: | EP1C6F324I7 |

| 廠商: | Altera Corporation |

| 英文描述: | Cyclone FPGA Family |

| 中文描述: | 氣旋FPGA系列 |

| 文件頁數(shù): | 40/94頁 |

| 文件大小: | 1138K |

| 代理商: | EP1C6F324I7 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁當(dāng)前第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁

40

Altera Corporation

Cyclone FPGA Family Data Sheet

Preliminary Information

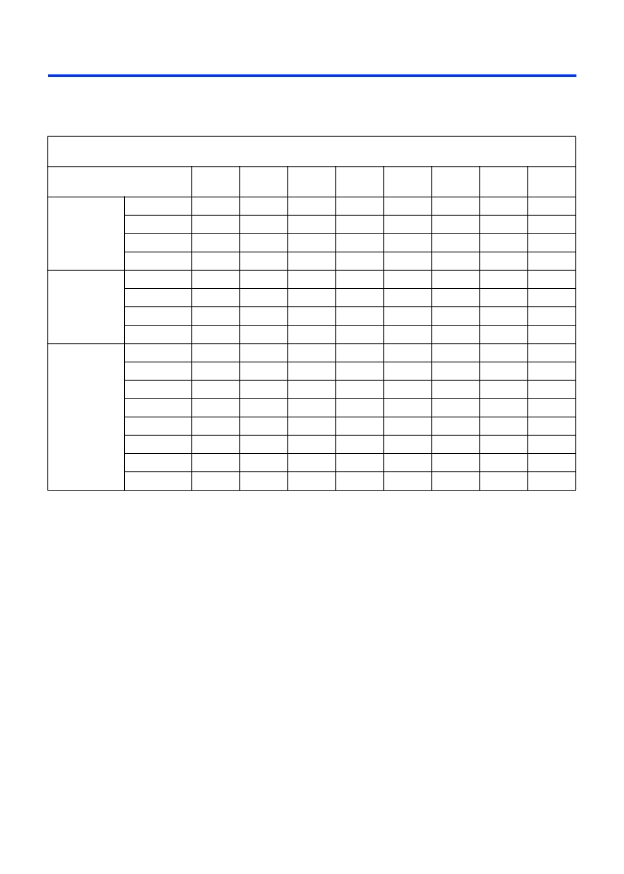

Table 10

shows the global clock network sources available in Cyclone

devices.

Notes to

Table 10

:

(1)

EP1C3 devices only have one PLL (PLL 1).

(2)

EP1C3 devices in the 100-pin TQFP package do not have dedicated clock pins

CLK1

and

CLK3

.

EP1C3 devices in the 100-pin TQFP package do not have the

DPCLK0

,

DPCLK1

, or

DPCLK5

pins.

Clock Multiplication & Division

Cyclone PLLs provide clock synthesis for PLL output ports using

m

/(

n

×

post scale counter) scaling factors. The input clock is divided by a

pre-scale divider,

n

, and is then multiplied by the

m

feedback factor. The

control loop drives the VCO to match f

IN

×

(

m

/

n

). Each output port has a

unique post-scale counter to divide down the high-frequency VCO. For

multiple PLL outputs with different frequencies, the VCO is set to the

least-common multiple of the output frequencies that meets its frequency

specifications. Then, the post-scale dividers scale down the output

frequency for each output port. For example, if the output frequencies

required from one PLL are 33 and 66 MHz, the VCO is set to 330 MHz (the

least-common multiple in the VCO’s range).

Table 10. Global Clock Network Sources

Source

GCLK0

GCLK1

GCLK2

GCLK3

GCLK4

GCLK5

GCLK6

GCLK7

PLL Counter

Output

PLL1 G0

v

v

PLL1 G1

v

v

PLL2 G0

(1)

v

v

PLL2 G1

(1)

v

v

Dedicated

Clock Input

Pins

CLK0

v

v

CLK1

(2)

v

v

CLK2

v

v

CLK3

(2)

v

v

Dual-Purpose

Clock Pins

DPCLK0

(3)

v

DPCLK1

(3)

v

DPCLK2

v

DPCLK3

v

DPCLK4

v

DPCLK5

(3)

v

DPCLK6

v

DPCLK7

v

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EP1C6F324I8 | Cyclone FPGA Family |

| EP1C6F400C6 | Cyclone FPGA Family |

| EP1C6F400C7 | Cyclone FPGA Family |

| EP1C6F400C8 | Cyclone FPGA Family |

| EP1C6F400I6 | Cyclone FPGA Family |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP1C6Q240C6 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Cyclone I 598 LABs 185 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP1C6Q240C6N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Cyclone I 598 LABs 185 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP1C6Q240C7 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Cyclone I 598 LABs 185 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP1C6Q240C7N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Cyclone I 598 LABs 185 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EP1C6Q240C8 | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Cyclone I 598 LABs 185 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。