- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄362685 > EM78P5830ADQ (ELAN Microelctronics Corp .) 8-BIT MICRO-CONTROLLER PDF資料下載

參數(shù)資料

| 型號(hào): | EM78P5830ADQ |

| 廠商: | ELAN Microelctronics Corp . |

| 英文描述: | 8-BIT MICRO-CONTROLLER |

| 中文描述: | 8位微控制器 |

| 文件頁(yè)數(shù): | 12/43頁(yè) |

| 文件大?。?/td> | 396K |

| 代理商: | EM78P5830ADQ |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)

EM785830AA

8-bit Micro-controller

__________________________________________________________________________________________________________________________________________________________________

* This specification is subject to be changed without notice.

12/1/2004 V1.6

Fsco=0.895MHz/2

If PLL is disabled, the instruction clock is 32.768kHz/2

Fsco=32.768kHz/2.

Bit 3 (SCES) : SPI clock edge selection bit

1

Data shifts out on falling edge, and shifts in on rising edge. Data is hold during the high level.

0

Data shifts out on rising edge, and shifts in on falling edge. Data is hold during the low level.

Bit 4 (SE) : SPI shift enable bit

1

Start to shift, and keep on 1 while the current byte is still being transmitted.

0

Reset as soon as the shifting is complete, and the next byte is ready to shift.

<Note> This bit has to be reset in software.

Bit 5 (SRO) : SPI read overflow bit

1

A new data is received while the previous data is still being hold in the SPIB register. In this situation,

the data in SPIS register will be destroyed. To avoid setting this bit, users had better to read SPIB

register even if the transmission is implemented only.

0

No overflow, <Note> This can only occur in slave mode.

Bit 6 (SPIE) : SPI enable bit

1

Enable SPI mode

0

Disable SPI mode

Bit 7 (RBF) : SPI read buffer full flag

1

Receive is finished, SPIB is full.

0

Receive is not finish yet, SPIB is empty.

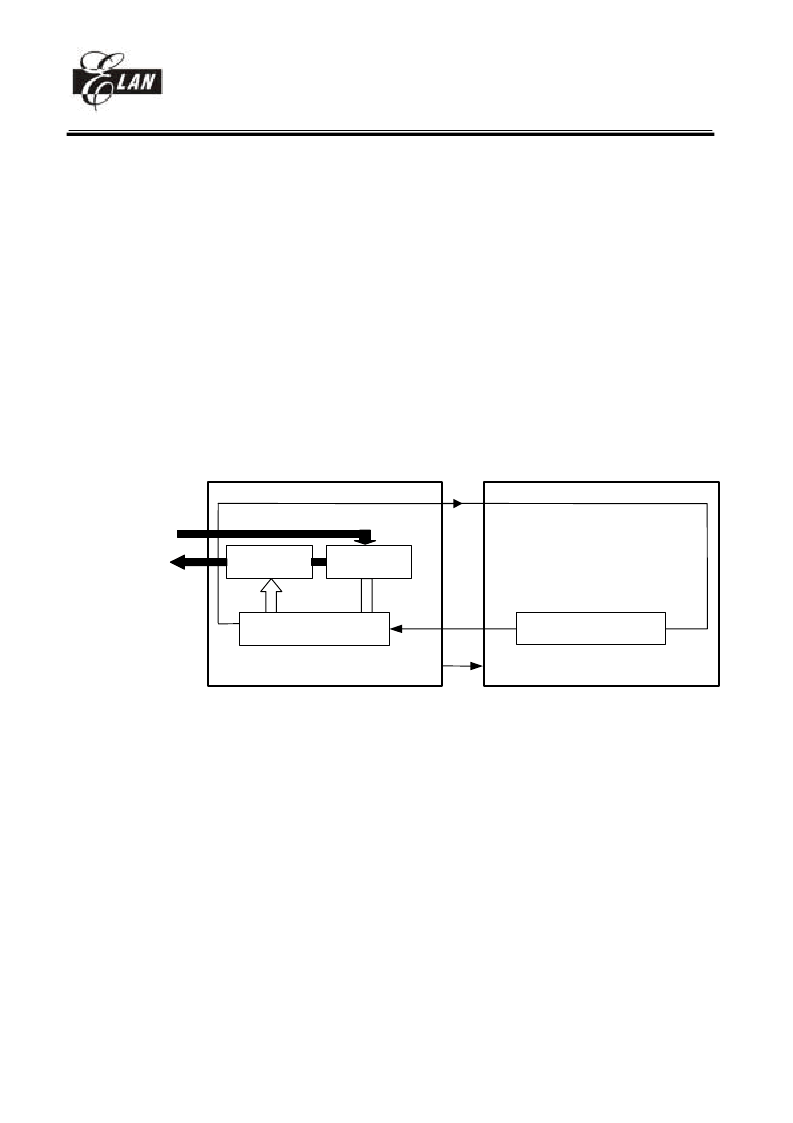

Bit 0

SPI module

SCK

Bit7

Salve Device

SPIR register

SDI

SPIW register

SPIS Reg

SDO

SDO

SCK

SDI

Master Device

R5 page1

Fig.4 Single SPI Master / Salve Communication

Fig. 4 shows how SPI to communicate with other device by SPI module. If SPI is a master controller, it

sends clock through the SCK pin. An 8-bit data is transmitted and received at the same time. If SPI,

however, is defined as a slave, its SCK pin could be programmed as an input pin. Data will continue to be

shifted on a basis of both the clock rate and the selected edge.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EM78P5830AM | 8-BIT MICRO-CONTROLLER |

| EM78P5830AP | 8-BIT MICRO-CONTROLLER |

| EM78P5830DQ | 8-BIT MICRO-CONTROLLER |

| EM785840 | 8-BIT MICRO-CONTROLLER |

| EM785840M | 8-BIT MICRO-CONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EM7A8620 | 制造商:EMC 制造商全稱(chēng):ELAN Microelectronics Corp 功能描述:Voice over IP |

| EM7G | 制造商:GULFSEMI 制造商全稱(chēng):Gulf Semiconductor 功能描述:ULTRAFAST EFFICIENT PLASTIC SILICON RECTIFIER VOLTAGE: 1000V CURRENT: 1.0A |

| EM800 | 制造商:EDI 制造商全稱(chēng):Electronic devices inc. 功能描述:HIGH VOLTAGE HIGH CURRENT MINIATURE RECTIFIERS |

| EM8000EHP | 制造商:JDSU 制造商全稱(chēng):JDS Uniphase Corporation 功能描述:The industrya??s most compact 100 G test solution |

| EM800-DCM | 制造商:MRV 制造商全稱(chēng):MRV 功能描述:LambdaDriver Dispersion Compensation Module (EM800/1600-DCM and DCMD) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。