- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378593 > DSPB56720AG (飛思卡爾半導(dǎo)體(中國)有限公司) SymphonyTM DSP56720 / DSP56721 Multi-Core Audio Processors PDF資料下載

參數(shù)資料

| 型號: | DSPB56720AG |

| 廠商: | 飛思卡爾半導(dǎo)體(中國)有限公司 |

| 英文描述: | SymphonyTM DSP56720 / DSP56721 Multi-Core Audio Processors |

| 中文描述: | SymphonyTM DSP56720 / DSP56721多核音頻處理器 |

| 文件頁數(shù): | 14/54頁 |

| 文件大小: | 671K |

| 代理商: | DSPB56720AG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁

Symphony

TM

DSP56720 / DSP56721 Multi-Core Audio Processors, Rev.1

Freescale Semiconductor

14

2.1.8

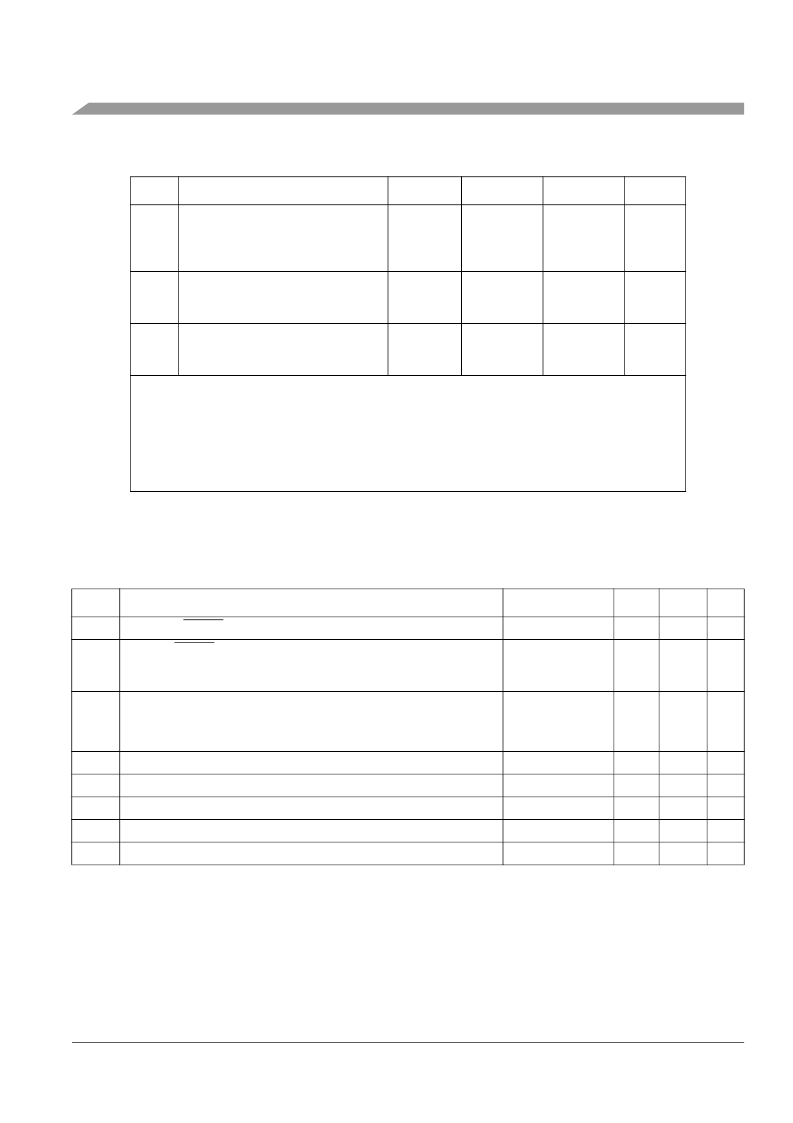

Reset, Stop, Mode Select, and Interrupt Timing

For reset, stop, mode select, and interrupt timing, see

Table 9

.

2

EXTAL input low

1

(40% to 60% duty cycle)

Crystal oscillator

Square wave input

Etl

16.67

2.5

100

inf

ns

3

EXTAL cycle time

With PLL disabled

With PLL enabled

Etc

5

33.3

inf

500

ns

4

Instruction cycle time

With PLL disabled

With PLL enabled

Tc

5.00

5.00

inf

5120

ns

Notes:

1.

2.

Measured at 50% of the input transition.

The indicated duty cycle is for the specified maximum frequency for which a part is rated. The minimum clock

high or low time required for correct operation, however, remains the same at lower operating frequencies;

therefore, when a lower clock frequency is used, the signal symmetry may vary from the specified duty cycle

as long as the minimum high time and low time requirements are met.

A valid clock signal must be applied to the EXTAL pin

within 3 ms

of the DSP56720/DSP56721 being

powered up.

3.

Table 9. Reset, Stop, Mode Select, and Interrupt Timing Parameters

No.

Characteristics

Expression

Min

Max

Unit

10

Delay from RESET assertion to all pins at reset value

3

–

–

11

ns

11

Required RESET duration

4

Power on, external clock generator, PLL disabled

Power on, external clock generator, PLL enabled

2 x T

C

2 x T

C

10

10

–

–

ns

ns

13

Syn reset deassert delay time

Minimum

2

×

T

C

10

–

ns

Maximum (PLL enabled)

(2 x T

C

) + T

LOCK

200

–

us

14

Mode select setup time

–

10.0

–

ns

15

Mode select hold time

–

10.0

–

ns

16

Minimum edge-triggered interrupt request assertion width

–

4

–

ns

17

Minimum edge-triggered interrupt request deassertion width

–

4

–

ns

18

Delay from interrupt trigger to interrupt code execution

10

×

T

C + 4

54

–

ns

Table 8. Clock Operation (Continued)

No.

Characteristics

Symbol

Min

Max

Units

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DSPB56721AF | SymphonyTM DSP56720 / DSP56721 Multi-Core Audio Processors |

| DSPB56721AG | SymphonyTM DSP56720 / DSP56721 Multi-Core Audio Processors |

| DSP56800ERM | 16-bit Digital Signal Controllers |

| DSP56800E | Digitial Signal Controller |

| DSP56853 | Digitial Signal Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DSPB56720CAG | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC 24-BIT 200MHz RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| DSPB56721AF | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC DSP56721 RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| DSPB56721AG | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC DSP56721 RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| DSPB56721AG | 制造商:Freescale Semiconductor 功能描述:Multi-Core Audio Digital Signal Processo |

| DSPB56721CAF | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC 24-BIT 200MHz RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。