- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄8542 > DS4422N+ (Maxim Integrated Products)IC DAC 7BIT 2CH 5.5V 14-TDFN PDF資料下載

參數(shù)資料

| 型號(hào): | DS4422N+ |

| 廠商: | Maxim Integrated Products |

| 文件頁(yè)數(shù): | 9/11頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC DAC 7BIT 2CH 5.5V 14-TDFN |

| 標(biāo)準(zhǔn)包裝: | 472 |

| 位數(shù): | 7 |

| 轉(zhuǎn)換器數(shù)目: | 2 |

| 電壓電源: | 單電源 |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 14-WFDFN 裸露焊盤(pán) |

| 供應(yīng)商設(shè)備封裝: | 14-TDFN-EP(3x3) |

| 包裝: | 管件 |

| 輸出數(shù)目和類型: | 2 電流,單極 |

| 采樣率(每秒): | * |

DS4422/DS4424

Two-/Four-Channel, I2C, 7-Bit Sink/Source

Current DAC

_______________________________________________________________________________________

7

Example: RFS0 = 80k

Ω and register 0xF8h is written to

a value of 0xAAh. Calculate the output current.

IFS = (0.976V/80k

Ω) x (127/16) = 96.838A

The MSB of the output register is 1, so the output is

sourcing the value corresponding to position 2Ah (42

decimal). The magnitude of the output current is equal to:

96.838A x (42/127) = 32.025A

I2C Serial Interface Description

I2C Definitions

The following terminology is commonly used to describe

I2C data transfers:

I2C Slave Address: The slave address of the

DS4422/DS4424 is determined by the state of the A0

and A1 pins (see Table 1).

Master Device: The master device controls the slave

devices on the bus. The master device generates SCL

clock pulses and START and STOP conditions.

Slave Devices: Slave devices send and receive data

at the master’s request.

Bus Idle or Not Busy: Time between STOP and START

conditions when both SDA and SCL are inactive and in

their logic-high states. When the bus is idle it often initi-

ates a low-power mode for slave devices.

START Condition: A START condition is generated by

the master to initiate a new data transfer with a slave.

Transitioning SDA from high to low while SCL remains

high generates a START condition. See Figure 1 for

applicable timing.

STOP Condition: A STOP condition is generated by the

master to end a data transfer with a slave. Transitioning

SDA from low to high while SCL remains high generates

a STOP condition. See Figure 1 for applicable timing.

Repeated START Condition: The master can use a

repeated START condition at the end of one data trans-

fer to indicate that it will immediately initiate a new data

transfer following the current one. Repeated STARTs are

commonly used during read operations to identify a spe-

cific memory address to begin a data transfer. A repeat-

ed START condition is issued identically to a normal

START condition. See Figure 1 for applicable timing.

Bit Write: Transitions of SDA must occur during the low

state of SCL. The data on SDA must remain valid and

unchanged during the entire high pulse of SCL, plus the

setup and hold time requirements (Figure 1). Data is

shifted into the device during the rising edge of the SCL.

Bit Read: At the end of a write operation, the master must

release the SDA bus line for the proper amount of setup

time (Figure 1) before the next rising edge of SCL during a

bit read. The device shifts out each bit of data on SDA at

the falling edge of the previous SCL pulse and the data bit

is valid at the rising edge of the current SCL pulse.

Remember that the master generates all SCL clock puls-

es, including when it is reading bits from the slave.

Acknowledgement (ACK and NACK): An Acknowledge-

ment (ACK) or Not Acknowledge (NACK) is always the

ninth bit transmitted during a byte transfer. The device

receiving data (the master during a read or the slave

during a write operation) performs an ACK by transmit-

ting a zero during the ninth bit. A device performs a

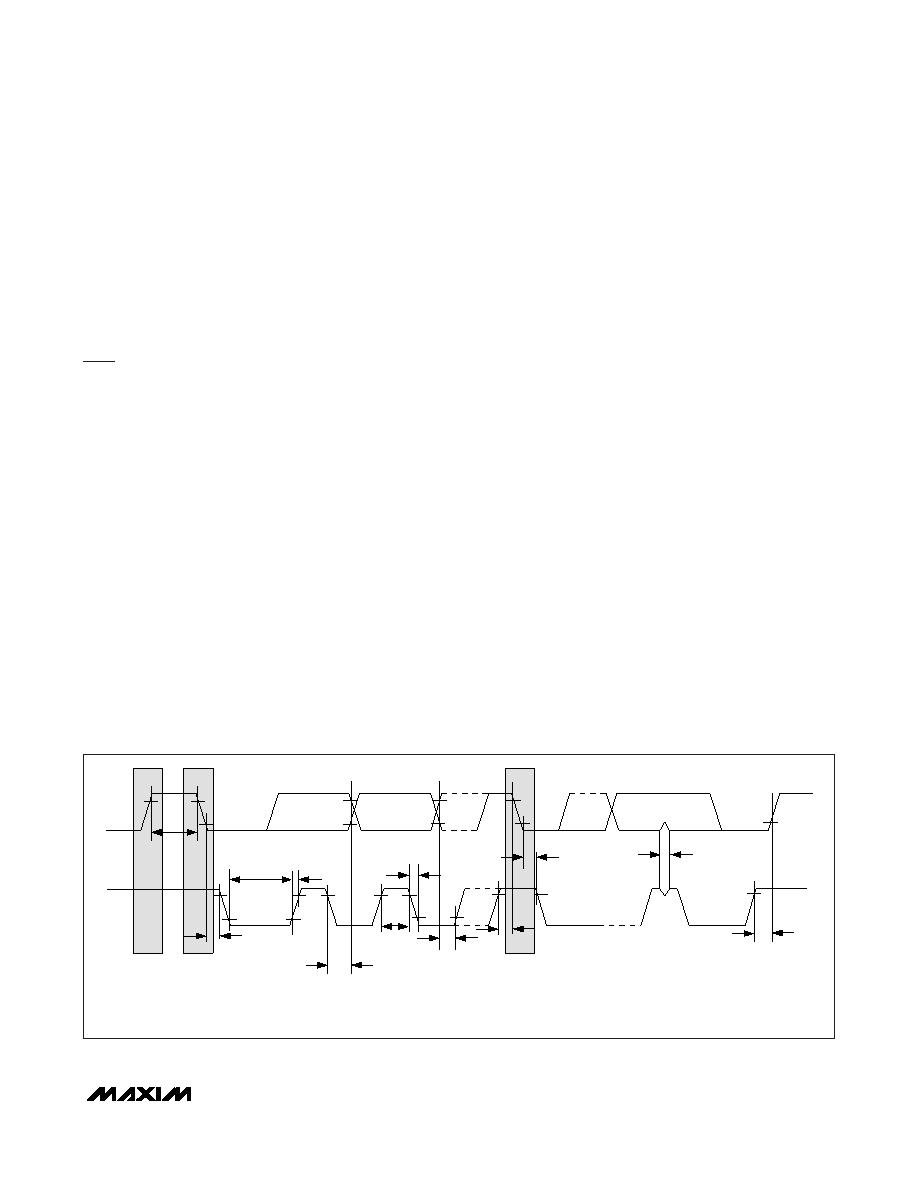

Figure 1. I2C Timing Diagram

SDA

SCL

tHD:STA

tLOW

tHIGH

tR

tF

tBUF

tHD:DAT

tSU:DAT

REPEATED

START

tSU:STA

tHD:STA

tSU:STO

tSP

STOP

NOTE: TIMING IS REFERENCED TO VIL(MAX) AND VIH(MIN).

START

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VE-J10-MW-S | CONVERTER MOD DC/DC 5V 100W |

| VE-JTL-MW-S | CONVERTER MOD DC/DC 28V 100W |

| DS4402N+T&R | IC DAC 2CH I2C ADJ 14-TDFN |

| VE-JT4-MW-S | CONVERTER MOD DC/DC 48V 100W |

| VE-JT3-MW-S | CONVERTER MOD DC/DC 24V 100W |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS4422N+ | 功能描述:數(shù)模轉(zhuǎn)換器- DAC 2Ch I2C 7-Bit Sink-Source RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時(shí)間:1 us 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| DS4422N+T&R | 制造商:Maxim Integrated Products 功能描述:LOW CURR 2 CH SINK/SRC CURR DAC LF - Tape and Reel 制造商:Maxim Integrated Products 功能描述:IC DAC 7BIT 2CH 5.5V 14-TDFN |

| DS4422N+T&R | 功能描述:數(shù)模轉(zhuǎn)換器- DAC 2Ch I2C 7-Bit Sink-Source RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時(shí)間:1 us 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| DS4422N+TR | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:Two-/Four-Channel, I2C, 7-Bit Sink/Source Current DAC |

| DS4424 | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:Two-/Four-Channel, I2C, 7-Bit Sink/Source Current DAC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。