- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358701 > DS1543P 64K NV Real Time Clocks RAM PDF資料下載

參數(shù)資料

| 型號: | DS1543P |

| 英文描述: | 64K NV Real Time Clocks RAM |

| 中文描述: | 64K的非易失RAM的實時時鐘 |

| 文件頁數(shù): | 3/17頁 |

| 文件大?。?/td> | 199K |

| 代理商: | DS1543P |

DS1543

3 of 17

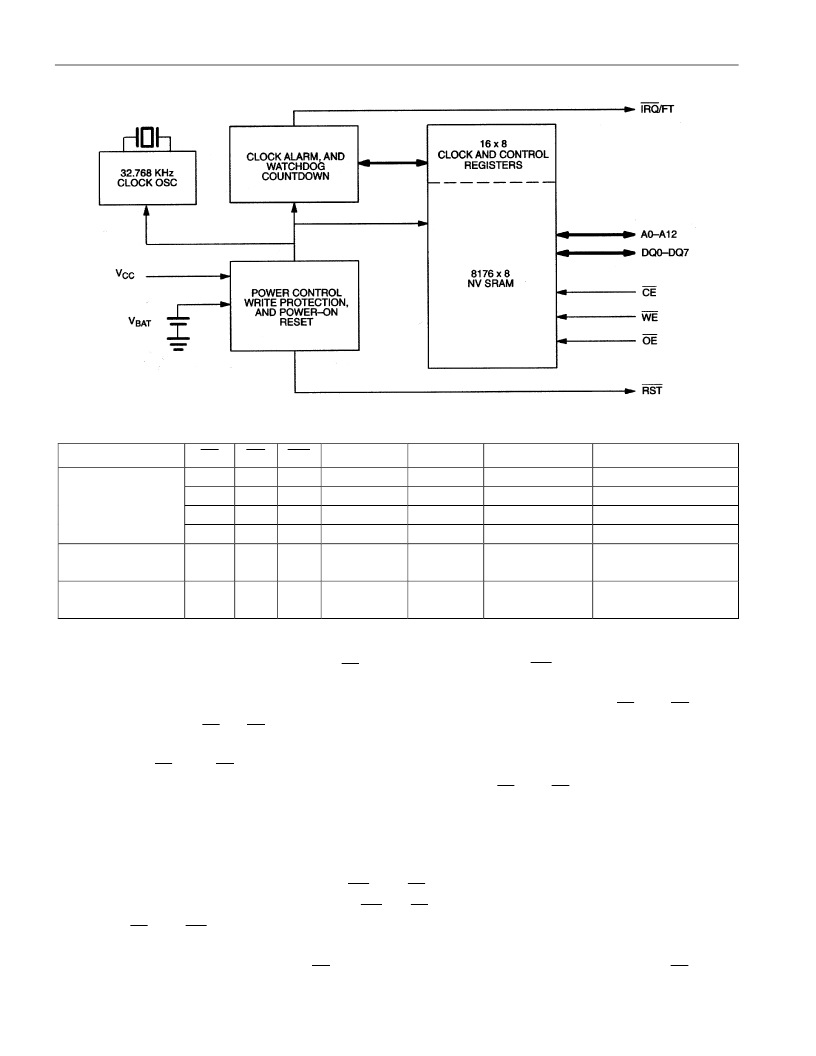

DS1543 BLOCK DIAGRAM

Figure 1

DS1543 OPERATING MODES

Table 1

V

CC

CE

V

IH

V

IL

V

IL

V

IL

V

BAT

< V

CC

<

Tolerance

<V

BAT

X

OE

X

X

V

IL

V

IH

X

WE

X

V

IL

V

IH

V

IH

X

DQ0-DQ7

HIGH-Z

D

IN

D

OUT

HIGH-Z

HIGH-Z

A0-A12

X

A

IN

A

IN

A

IN

X

MODE

DESELECT

WRITE

READ

READ

DESELECT

POWER

STANDBY

ACTIVE

ACTIVE

ACTIVE

CMOS STANDBY

In Tolerance

X

X

X

HIGH-Z

X

DATA

RETENTION

BATTERY

CURRENT

DATA READ MODE

The DS1543 is in the read mode whenever

CE

(chip enable) is low and

WE

(write enable) is high. The

device architecture allows ripple through access to any valid address location. Valid data will be

available at the DQ pins within t

AA

after the last address input is stable, providing that

CE

and

OE

access

times are satisfied. If

CE

or

OE

access times are not met, valid data will be available at the latter of chip

enable access (t

CEA

) or at output enable access time (t

OEA

). The state of the data input/output pins (DQ) is

controlled by

CE

and

OE

. If the outputs are activated before t

AA

, the data lines are driven to an

intermediate state until t

AA

. If the address inputs are changed while

CE

and

OE

remain valid, output data

will remain valid for output data hold time (t

OH

) but will then go indeterminate until the next address

access.

DATA WRITE MODE

The DS1543 is in the write mode whenever

WE

and

CE

are in their active state. The start of a write is

referenced to the latter occurring transition of

WE

or

CE

. The addresses must be held valid throughout

the cycle.

CE

and

WE

must return inactive for a minimum of t

WR

prior to the initiation of a subsequent

read or write cycle. Data in must be valid t

DS

prior to the end of the write and remain valid for t

DH

afterward. In a typical application, the

OE

signal will be high during a write cycle. However,

OE

can be

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DS1554-100 | 256K NV Y2KC Timekeeping RAM |

| DS1554-70 | 256K NV Y2KC Timekeeping RAM |

| DS1554W-120 | 256K NV Y2KC Timekeeping RAM |

| DS1554 | 256K NV Y2KC Timekeeping RAM |

| DS1554P-70 | 256K NV Y2KC Timekeeping RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS1543P-100 | 功能描述:實時時鐘 RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 總線接口:I2C 日期格式:DW:DM:M:Y 時間格式:HH:MM:SS RTC 存儲容量:64 B 電源電壓-最大:5.5 V 電源電壓-最小:1.8 V 最大工作溫度:+ 85 C 最小工作溫度: 安裝風(fēng)格:Through Hole 封裝 / 箱體:PDIP-8 封裝:Tube |

| DS1543P-100+ | 功能描述:實時時鐘 RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 總線接口:I2C 日期格式:DW:DM:M:Y 時間格式:HH:MM:SS RTC 存儲容量:64 B 電源電壓-最大:5.5 V 電源電壓-最小:1.8 V 最大工作溫度:+ 85 C 最小工作溫度: 安裝風(fēng)格:Through Hole 封裝 / 箱體:PDIP-8 封裝:Tube |

| DS1543P-70 | 功能描述:實時時鐘 RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 總線接口:I2C 日期格式:DW:DM:M:Y 時間格式:HH:MM:SS RTC 存儲容量:64 B 電源電壓-最大:5.5 V 電源電壓-最小:1.8 V 最大工作溫度:+ 85 C 最小工作溫度: 安裝風(fēng)格:Through Hole 封裝 / 箱體:PDIP-8 封裝:Tube |

| DS1543P-85 | 功能描述:實時時鐘 RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 總線接口:I2C 日期格式:DW:DM:M:Y 時間格式:HH:MM:SS RTC 存儲容量:64 B 電源電壓-最大:5.5 V 電源電壓-最小:1.8 V 最大工作溫度:+ 85 C 最小工作溫度: 安裝風(fēng)格:Through Hole 封裝 / 箱體:PDIP-8 封裝:Tube |

| DS1543P-85+ | 功能描述:實時時鐘 RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 總線接口:I2C 日期格式:DW:DM:M:Y 時間格式:HH:MM:SS RTC 存儲容量:64 B 電源電壓-最大:5.5 V 電源電壓-最小:1.8 V 最大工作溫度:+ 85 C 最小工作溫度: 安裝風(fēng)格:Through Hole 封裝 / 箱體:PDIP-8 封裝:Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。