- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄223666 > DR-11800D4-164W (DATA DEVICE CORP) DIGITAL TO SYNCHRO OR RESOLVER, CQIP28 PDF資料下載

參數(shù)資料

| 型號(hào): | DR-11800D4-164W |

| 廠商: | DATA DEVICE CORP |

| 元件分類(lèi): | 位置變換器 |

| 英文描述: | DIGITAL TO SYNCHRO OR RESOLVER, CQIP28 |

| 封裝: | 1 X 1 INCH, 0.210 INCH HEIGHT, HERMETIC SEALED PACKAGE-28 |

| 文件頁(yè)數(shù): | 4/8頁(yè) |

| 文件大小: | 350K |

| 代理商: | DR-11800D4-164W |

4

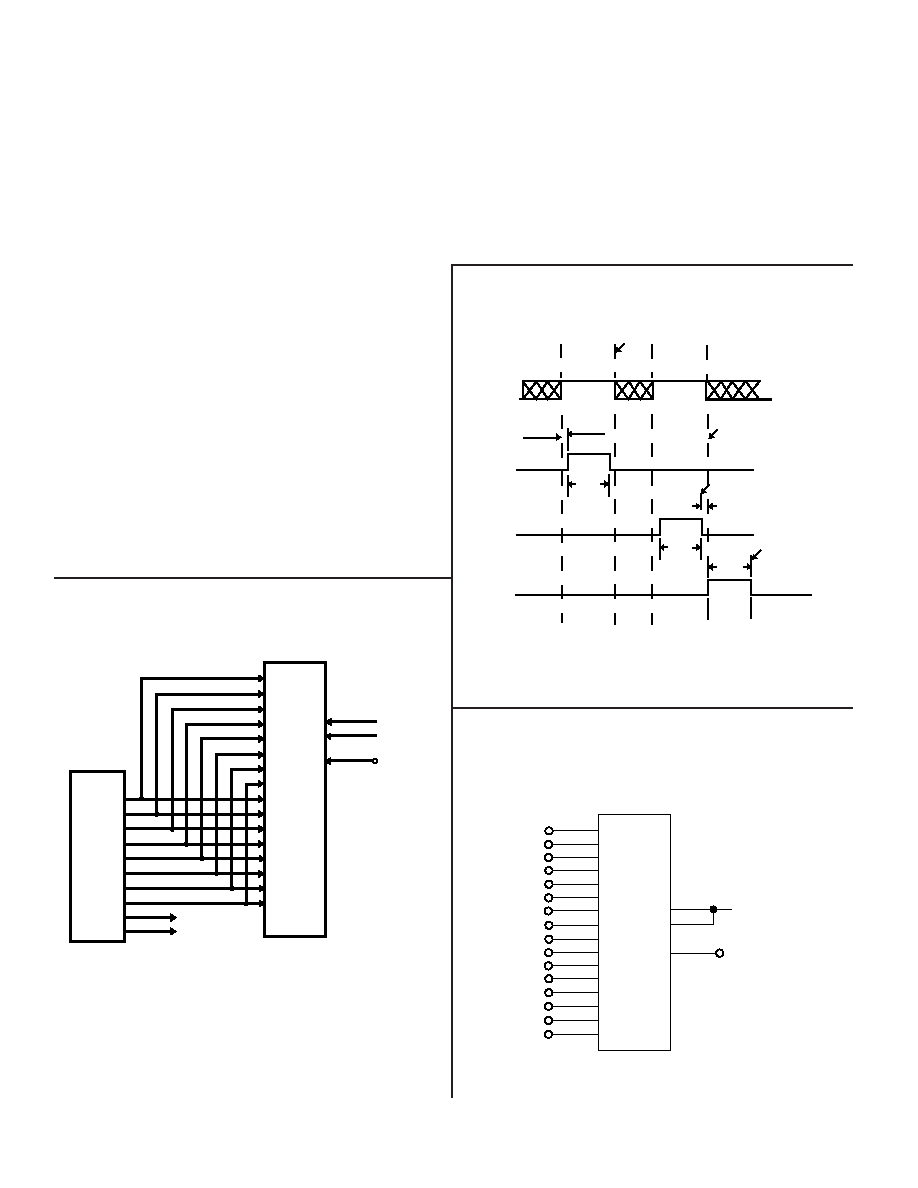

DATA TRANSFER FROM AN 8-BIT DATA BUS

Applications with an 8-bit data bus require two-byte loading of

the digital input (see FIGURE 4).

FIGURE 5 shows the timing for two-byte data transfers.

1. LDC is low (logic 0) so that the contents of the holding regis-

ter are latched and will remain unaffected by the changes on the

input registers.

2.When the LBE is set high (logic 1) the 8 LSBs (B9-B16) are

transferred to the low byte. The LBE must remain high for a min-

imum of 800 nsec after the data is stable. The data should

remain stable for 200 nsec after the LBE is set low (logic 0).

3.When the HBE is set high (logic 1) the 8 MSBs (B1-B8) are

transferred to the low byte. The HBE must remain high for a min-

imum of 800 nsec after the data is stable. The data should

remain stable for 200 nsec after the HBE is set low (logic 0).

4.When the LDC is set high (logic 1) the data is transferred from

the two input registers to the holding register. The LDC should

be held high for 600 nsec minimum. Once the LDC is set low,

the cycle can begin again.

Note: LBE, HBE, and LDC are level-actuated functions.

DATA TRANSFER FROM A 16-BIT DATA BUS

Applications interfacing with a 16-bit data bus require only single

byte loading, as shown in FIGURE 6. LBE and HBE are either

unconnected or tied together and pulsed high to load data.

As shown in the timing diagram (see FIGURE 7) 200 nsec after

the data is stable the LDC is set high (logic 1) to transfer the data

to the holding register.

Since LDC is level actuated, it must

remain high for the time specified (600 nsec) to transfer the data.

B1

B2

B3

B4

B5

B6

B13

B12

B11

B10

B9

B8

B7

B14

B15

B16

(LSB)

(MSB)

1

2

3

4

5

6

7

8

11

12

13

14

15

16

17

18

DR-11800

LBE

HBE

LDC

LOAD

CONVERTER

NOT CONNECTED

OR LOAD DATA PULSE

10

9

19

FIGURE 6. DATA TRANSFER FROM 16-BIT BUS

1

12

4

3

2

5

6

7

8

11

13

14

15

16

17

18

LBE

HBE

LDC

LOAD

CONVERTER

LOAD MSBs

LOAD LSBs

DR-11800

(MSB)

(LSB)

D7

D1

D2

D3

D4

D5

D6

D0

HBE

LBE

DATA BUS

PULSE

WIDTH

600 ns

MIN

PULSE

WIDTH

600ns

MIN

DATA TRANSFERRED TO

HOLDING REGISTERS

8 MSBs TRANSFERRED

TO INPUT REGISTERS

DATA

CHANGING

DATA

STEADY

(LSBs)

DATA SET UP

200 ns

MIN

DATA HOLD

200ns

MIN

(MSBs)

8 LSBs TRANSFERRED

TO INPUT REGISTERS

DATA

LBE

LDC

HBE

600 ns

MIN

FIGURE 5. TIMING FOR 8-BIT BUS TRANSFER

FIGURE 4. DATA TRANSFER FROM 8-BIT BUS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DR14-206 | BRASS, TIN FINISH, PUSH-ON TERMINAL |

| DR14-205 | BRASS, TIN FINISH, PUSH-ON TERMINAL |

| DRA618-GT-S-R | DIP18, IC SOCKET |

| DRC-10520-834S | DIGITAL TO SYNCHRO OR RESOLVER, DMA32 |

| DRC-10520-294S | DIGITAL TO SYNCHRO OR RESOLVER, DMA32 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DR-11800D4-164Y | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Converter |

| DR-11800D4-164Z | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Converter |

| DR-11800D4-165 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Converter |

| DR-11800D4-165K | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Converter |

| DR-11800D4-165L | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:Converter |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。