- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376760 > DM2240J2-10 Enhanced DRAM (EDRAM) PDF資料下載

參數(shù)資料

| 型號(hào): | DM2240J2-10 |

| 英文描述: | Enhanced DRAM (EDRAM) |

| 中文描述: | 增強(qiáng)的DRAM(eDRAM內(nèi)存) |

| 文件頁(yè)數(shù): | 2/21頁(yè) |

| 文件大小: | 124K |

| 代理商: | DM2240J2-10 |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)

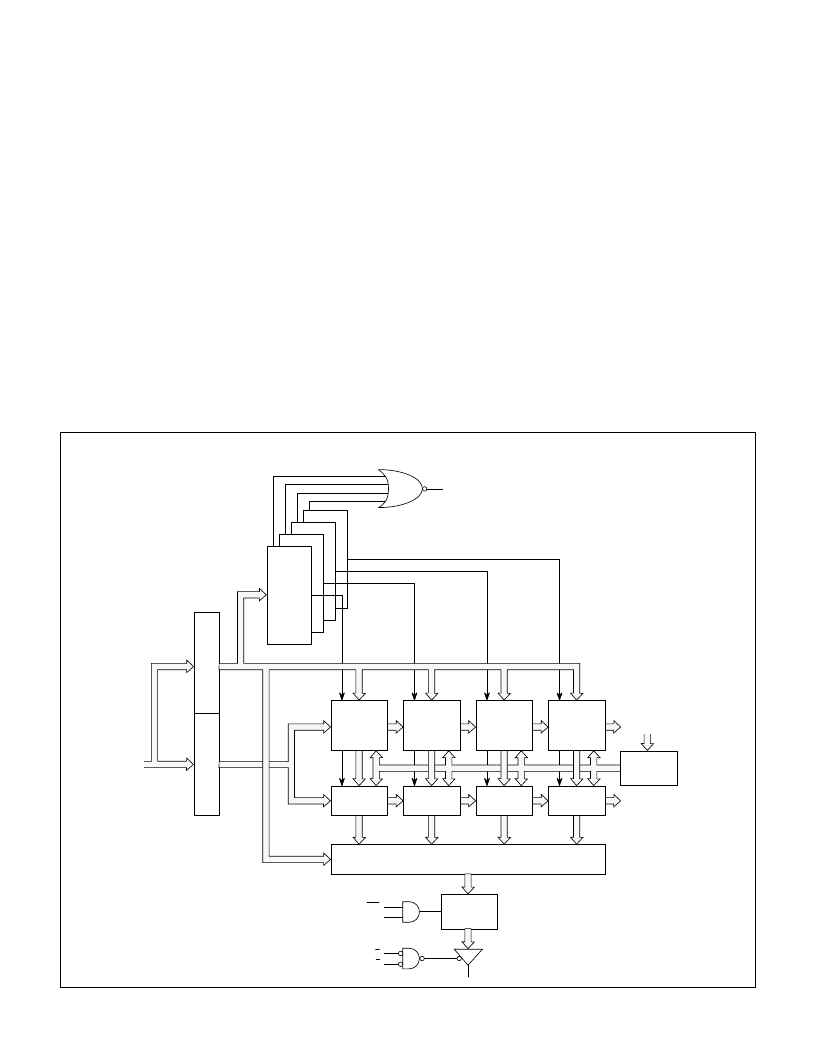

The EDRAMs SRAMcache is integrated into the DRAMarray

as tightly coupled rowregisters. The 512K x 8 EDRAMhas a total of

four independent DRAMmemory banks each wth its own 256 x 8

SRAMrowregister. Memory reads always occur fromthe cache

rowregister of one of these banks as specified by rowaddress bits

A

8

and A

9

(bank select). When the internal comparator detects that

the rowaddress matches the last rowread fromany of the four

DRAMbanks (page hit), the SRAMis accessed and data is available

on the output pins in 12ns fromcolumn address input. The /HIT

pin is driven lowduring a page hit to signify to the DRAMcontrol

logic that data is available early Subsequent reads wthin the page

(burst reads or randomreads) can continue at 12ns cycle time.

When the rowaddress does not match the last rowread fromany

of the four DRAMbanks (page mss), the newDRAMrowis

accessed and loaded into the appropriate SRAMrowregister and

data is available on the output pins all wthin 30ns fromrow

enable. In this case, the /HITpin is driven high to signify to the

control logic that data is available later. Subsequent reads wthin

the page (burst reads or randomreads) can continue at 12ns cycle

time. During either read hit or read mss operations, a user

controllable on-chip output data latch can be used to extend data

output time to allowuse of the full 83Mbyte/second bandwdth.

Since reads occur fromthe SRAMcache, the DRAMprecharge

can occur during burst reads. This elimnates the precharge time

delay suffered by other DRAMs and SDRAMs when accessing a new

page. The EDRAMhas an independent on-chip refresh counter and

dedicated refresh control pin to allowthe DRAMarray to be

refreshed concurrently wth cache read operations (hidden refresh).

During EDRAMread accesses, data can be accessed in either

static column or page mode depending upon the operation of the

/CAL input. If /CAL is held high, newdata is accessed wth each new

column address (static column mode). If /CAL is brought low

during a read access, the column address is latched and newdata

wll not be accessed until both the column address is changed and

/CAL is brought high (page mode). A dedicated output enable (/G)

wth 5ns access time allows high speed two-way interleave wthout

an external multiplexer.

Memory writes are posted to the input data latch and directed

to the DRAMarray During a write hit, the on-chip address

comparator activates a parallel write path to the SRAMcache to

maintain coherency Randomor page mode writes can be posted

5ns after column address and data are available. The EDRAM

allows 12ns page mode cycle time for both write hits and write

msses. Memory writes do not affect the contents of the cache row

2-36

Bank 3

Bank 2

Bank 1

CAL

QLE

R

C

Last

Row

Read

Address

Latch

+ 9-Bit

Compare

Bank 0

HIT0

HIT1

HIT2

HIT3

/HIT

1 of 4 Selector

(0,0)

(0,1)

(1,0)

(1,1)

D

0-7

Bank 0

Bank 1

Bank 2

Bank 3

CA

0-7

CA

0-7

RA

8

, RA

9

A

0-10

RA

0-10

Data-Out

Latch

G

S

Q

0-7

1M Array

1M Array

1M Array

1M Array

256 x 8

Cache

256 x 8

Cache

256 x 8

Cache

256 x 8

Cache

Data-In

Latch

Four Bank Cache Architecture

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DM2M32SJ6-10 | Enhanced DRAM (EDRAM) Module |

| DM2M36SJ-10 | Enhanced DRAM (EDRAM) Module |

| DM4M32SJ-10 | Enhanced DRAM (EDRAM) Module |

| DM2203T-20 | Enhanced DRAM (EDRAM) |

| DM2203TME-15 | Enhanced DRAM (EDRAM) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DM2240J2-12 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Enhanced DRAM (EDRAM) |

| DM2240J2-12I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Enhanced DRAM (EDRAM) |

| DM2240J2-12L | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Enhanced DRAM (EDRAM) |

| DM2240J2-15 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Enhanced DRAM (EDRAM) |

| DM2240J2-15I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Enhanced DRAM (EDRAM) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。