- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376760 > DM2213T-15 Enhanced DRAM (EDRAM) PDF資料下載

參數(shù)資料

| 型號(hào): | DM2213T-15 |

| 英文描述: | Enhanced DRAM (EDRAM) |

| 中文描述: | 增強(qiáng)的DRAM(eDRAM內(nèi)存) |

| 文件頁數(shù): | 3/21頁 |

| 文件大小: | 124K |

| 代理商: | DM2213T-15 |

2-37

register except during a cache hit. Since the DRAMarray can be

written to at SRAMspeeds, there is no need for complex writeback

schemes.

By integrating the SRAMcache as rowregisters in the DRAM

array and keeping the on-chip control simple, the EDRAMis able

to provide superior performance over standard slow4Mb DRAMs.

By elimnating the need for SRAMs and cache controllers, system

cost, board space, and power can all be reduced.

Functional Description

The EDRAMis designed to provide optimummemory

performance wth high speed mcroprocessors. As a result, it is

possible to performsimultaneous operations to the DRAMand

SRAMcache sections of the EDRAM This feature allows the EDRAM

to hide precharge and refresh operation during reads and

maximze hit rate by maintaining page cache contents during write

operations even if data is written to another memory page. These

capabilities, in conjunction wth the faster basic DRAMand cache

speeds of the EDRAM mnimze processor wait states.

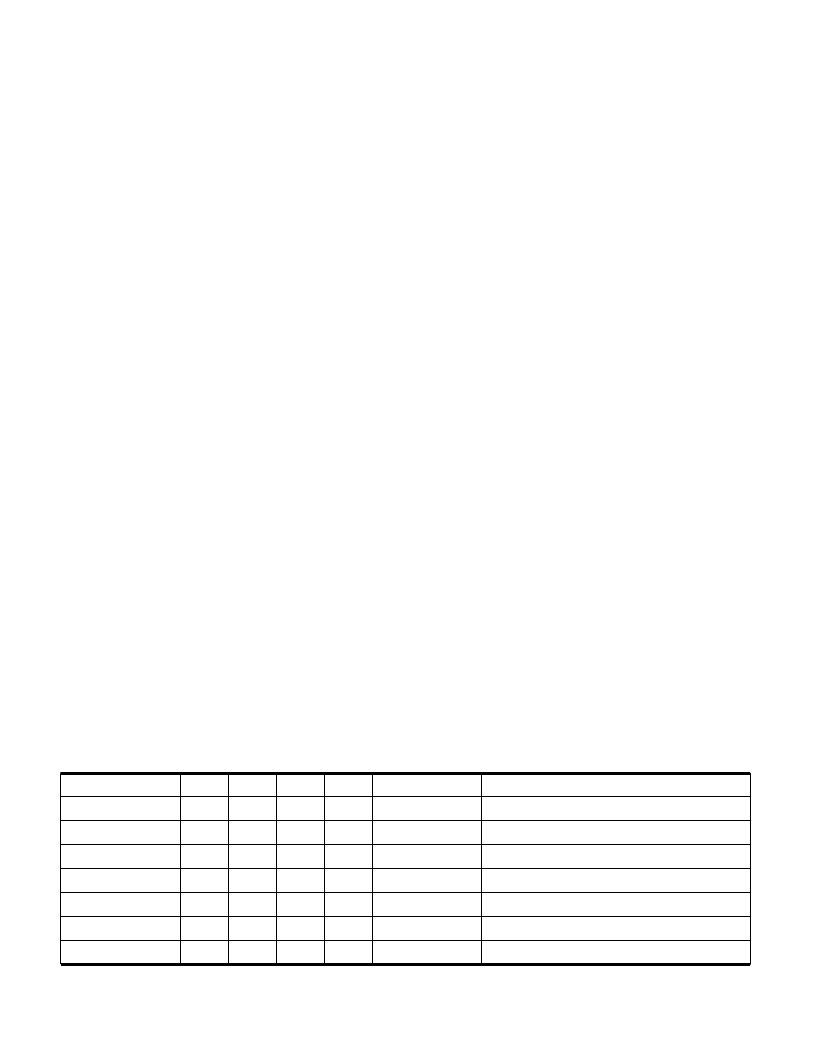

EDRAMBasic Operating Modes

The EDRAMoperating modes are specified in the table below

Ht andMss Termnology

In this datasheet, “hit” and “mss” always refer to a hit or mss

to any of the four pages of data contained in the SRAMcache row

registers. There are four cache rowregisters, one for each of the

four banks of DRAM These registers are specified by the bank

select rowaddress bits A

8

and A

9

. The contents of these cache row

registers is always equal to the last rowthat was read fromeach of

the four internal DRAMbanks (as modified by any write hit data).

DRAMReadHt

A DRAMread request is initiated by clocking /RE wth W/R low

and /F high. The EDRAMwll compare the newrowaddress to the

last rowread address latch for the bank specified by rowaddress

bits A

8-9

(LRR: a 9-bit rowaddress latch for each internal DRAM

bank which is reloaded on each /RE active read mss cycle). If the

rowaddress matches the LRR, the requested data is already in the

SRAMcache and no DRAMmemory reference is initiated. The data

specified by the rowand column address is available at the output

pins at the greater of times t

AC

or t

GQV

. The /HIT output is driven

lowat time t

HV

after /RE to indicate the shorter access time to the

external control logic. Since no DRAMactivity is initiated, /RE can

be brought high after time t

RE1

, and a shorter precharge time, t

RP1

,

is required. Additional locations wthin the currently active page

may be accessed concurrently wth precharge by providing new

column addresses to the multiplex address inputs. Newdata is

available at the output at time t

AC

after each column address change

in static column mode. During any read cycle, it is possible to

operate in either static column mode wth /CAL=high or page

mode wth /CAL clocked to latch the column address. In page

mode, data valid time is determned by either t

AC

and t

CQV

.

DRAMReadMss

A DRAMread request is initiated by clocking /RE wth W/R low

and /F high. The EDRAMwll compare the newrowaddress to the

LRR address latch for the bank specified by rowaddress bits A

8-9

(LRR: a 9-bit rowaddress latch for each internal DRAMbank

which is reloaded on each /RE active read mss cycle). If the row

address does not match the LRR, the requested data is not in SRAM

cache and a newrowis fetched fromthe DRAM The EDRAMwll

load the newrowdata into the SRAMcache and update the LRR

latch. The data at the specified column address is available at the

output pins at the greater of times t

, t

, and t

. The /HIT

output is driven high at time t

HV

after /RE to indicate the longer

access time to the external control logic. /RE may be brought high

since the newrowdata is safely latched into SRAM

cache. This allows the EDRAMto precharge the DRAMarray while

data is accessed fromSRAMcache. Additional locations wthin the

currently active page may be accessed by providing newcolumn

addresses to the multiplex address inputs. Newdata is available at

the output at time t

after each column address change in static

column mode. During any read cycle, it is possible to operate in

either static column mode wth /CAL=high or page mode wth /CAL

clocked to latch the column address. In page mode, data valid time

is determned by either t

AC

and t

CQV

.

DRAMWrite Ht

A DRAMwrite request is initiated by clocking /RE while W/R,

/CAL, /WE, and /F are high. The EDRAMwll compare the newrow

address to the LRR address latch for the bank specified by row

address bits A

8-9

(LRR: a 9-bit rowaddress latch for each internal

DRAMbank which is reloaded on each /RE active read mss cycle).

If the rowaddress matches the LRR, the EDRAMwll write data to

both the DRAMpage in the appropriate bank and its corresponding

SRAMcache simultaneously to maintain coherency The write

address and data are posted to the DRAMas soon as the column

address is latched by bringing /CAL lowand the write data is latched

by bringing /WE low(both /CAL and /WE must be high when

Function

/S

Read Hit

L

/RE

W/R

/F

A

0-10

Comment

L

H

Row = LRR

No DRAM Reference, Data in Cache

Read Miss

L

↓

L

H

Row

≠

LRR

DRAM Row to Cache

Write Hit

L

H

H

Row = LRR

Write to DRAM and Cache, Reads Enabled

Write Miss

L

H

H

Row

≠

LRR

Write to DRAM, Cache Not Updated, Reads Disabled

Internal Refresh

X

X

L

X

Low Power Standby

H

X

X

X

1mA Standby Current

Unallowed Mode

H

X

L

H

X

↓

↓

↓

H

↓

H = High; L = Low; X = Don’t Care; = High-to-Low Transition; LRR = Last Row Read

EDRAM Basic Operating Modes

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DM2213T-15I | Enhanced DRAM (EDRAM) |

| DM2213T-20 | Enhanced DRAM (EDRAM) |

| DM2213TME-15 | Enhanced DRAM (EDRAM) |

| DM2213TME-20 | Enhanced DRAM (EDRAM) |

| DM2240J2-10 | Enhanced DRAM (EDRAM) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DM2213T-15I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Enhanced DRAM (EDRAM) |

| DM2213T-20 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Enhanced DRAM (EDRAM) |

| DM2213TME-15 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Enhanced DRAM (EDRAM) |

| DM2213TME-20 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Enhanced DRAM (EDRAM) |

| DM2223T-12 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Enhanced DRAM (EDRAM) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。