- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379101 > CZ80CPU (Electronic Theatre Controls, Inc.) 8-Bit Microprocessor Megafunction PDF資料下載

參數(shù)資料

| 型號: | CZ80CPU |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 8-Bit Microprocessor Megafunction |

| 中文描述: | 8位微處理器宏功能 |

| 文件頁數(shù): | 3/5頁 |

| 文件大?。?/td> | 73K |

| 代理商: | CZ80CPU |

CZ80CPU Megafunction Datasheet

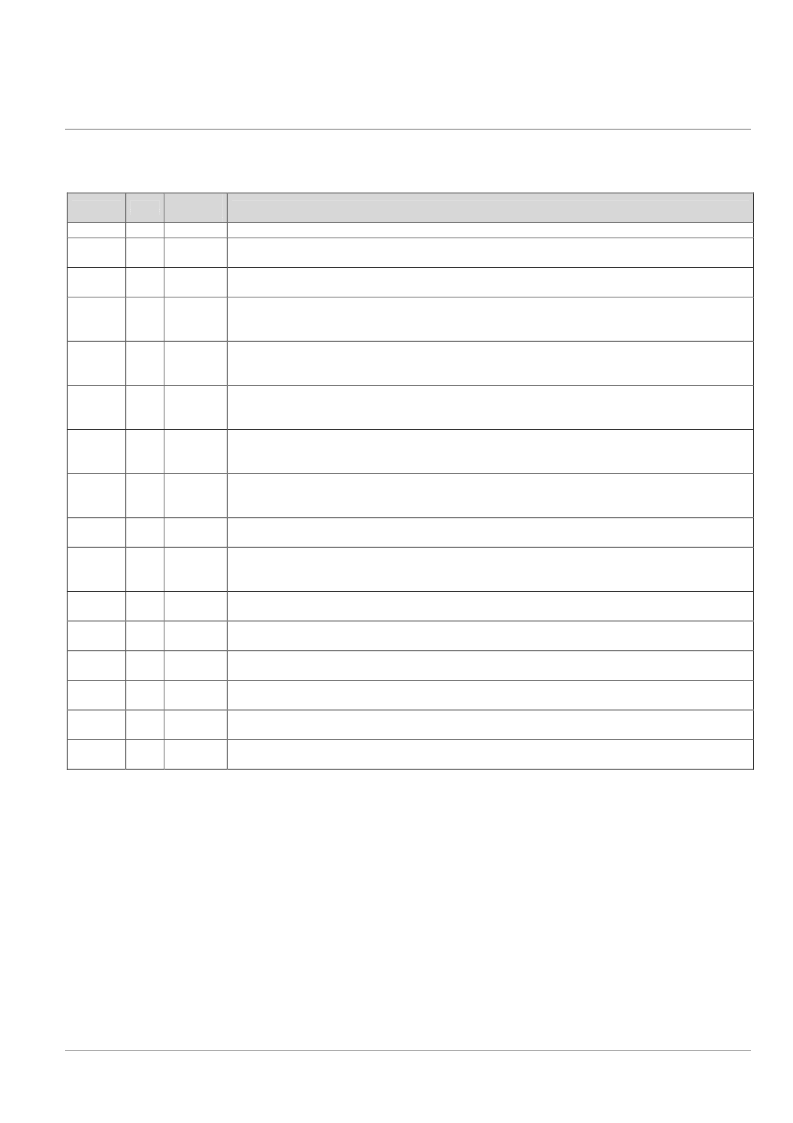

Pin Description

Name

Type Bus size

I

Rise

I

High

Description

clk

reset

Clock

Feeds internal clock counters and all synchronous circuits.

Hardware reset input

A high on this pin for two clock cycles while the oscillator is running

resets the device.

Wait

A low on this pin indicates to the CPU that the addressed memory or I/O devices are not

ready for a data transfer. The CPU continues to enter a wait state as long as this signal is active.

Interrupt Request

This signal is generated by an I/O device. The CPU honors a request at the

end of the current instruction, if the internal software-controlled interrupt enable flip-flop is

enabled.

Non-maskable Interrupt

This pin has a higher priority then int_n and is always recognized at

the end of the current instruction independent of the status of the interrupt enable flip-flop and

forced the CPU to restart at address 0066h.

Bus Request

It has higher priority than nmi_n and is always recognized at the end of the

current machine cycles. Active state on this pin forces the CPU address bus, data bus, and

control signal to go to a high-impedance state, so that other devices can control these lines.

Bus Request Acknowledgment

Low on this pin indicates to the requesting device that the

CPU address bus, data bus, and control signal have entered their high-impedance state and it

can now control these lines.

Machine Cycles One

This pin together with mreq_n indicates that the current machine cycle is

the opcode fetch cycle of an instruction execution. It together with iorq_n indicates an interrupt

acknowledge cycle.

Address Bus

Addr_o forms a 16-bit address bus. The address bus provides the address for

memory data bus exchanges (up to 64K bytes) and for I/O device exchanges.

Data Bus

(input/output, 3-state) 8-bit bidirectional data bus, used for data exchanges with

memory and I/O.

wait_n

I

Low

int_n

I

Low

nmi_n

I

Low

busreq_n I

Low

busak_n

O

Low

m1

O

High

addr_o

addr_tri

data_i

data_o

data_tri

mreq_n

mreq_tri

ioreq_n

ioreq_tri

rd_n

rd_tri

wr_n

wr_tri

rfsh_n

O

O

I

O

O

O

O

O

O

O

O

O

O

O

8

High

8

8

High

Low

High

Low

High

Low

High

Low

High

Low

Memory Request

Indicates that the address bus holds a valid address for memory read or

memory write operation.

I/ O Request

Indicates that the lower half of the address bus holds a valid I/O address for an

I/O read or write operation.

Read

rd_n indicates that the CPU wants to read data from memory, or that an I/O device or

memory should use this signal to gate data onto the CPU data bus.

Write

Indicates that the CPU data bus holds valid data to be stored at the addressed memory

or I/O device.

Refresh Timing

This signal together with mreq_n, indicates that the lower seven bits of the

system’s address bus can be used as a refresh address to the system’s dynamic memories.

Halt

State low on this pin indicates that the CPU has executed a Halt instruction and is awaiting

either a nonmaskable or a maskable interrupt before operation can resume.

halt_n

O

Low

Functional Description

The CZ80CPU core is partitioned into modules as shown in the Block Diagram and described below.

Cycle Control

The main control machine, which synchronizes all the others. It has an instruction register and all registers

controlled interrupts, bus request cycle, wait states etc. This unit controls bus control signals too.

Bus Control

Registers are triggered on the falling edge and or gates. These are used to form the bus control timing,

changed on both clock edges. This is the only unit that has registers synchronized on the falling clock edge.

CAST, Inc.

Page 3

相關PDF資料 |

PDF描述 |

|---|---|

| CZ80PIO | Hereinafter Referred to As PIO, is a Dual-Port Device |

| D048C033T015M1N | DC-DC Converters Quarter Brick, 48 Vin Family |

| D048C050T015M1N | DC-DC Converters Quarter Brick, 48 Vin Family |

| D048C015T012M2N | DC-DC Converters Quarter Brick, 48 Vin Family |

| D048C025T015M2N | DC-DC Converters Quarter Brick, 48 Vin Family |

相關代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CZ80PIO | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Hereinafter Referred to As PIO, is a Dual-Port Device |

| CZ8110 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| CZ8111 | 制造商:SPECTRUM 制造商全稱:Spectrum Microwave, Inc. 功能描述:RF AMPLIFIER |

| CZ8120 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| CZ8121-000 | 制造商:TE Connectivity 功能描述:55PC2241-16-CML4-9CS2970 - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。