- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379098 > CY8C27443-24SXIT (CYPRESS SEMICONDUCTOR CORP) PSoC Mixed Signal Array PDF資料下載

參數(shù)資料

| 型號(hào): | CY8C27443-24SXIT |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | 外設(shè)及接口 |

| 英文描述: | PSoC Mixed Signal Array |

| 中文描述: | MULTIFUNCTION PERIPHERAL, PDSO28 |

| 封裝: | 0.300 INCH, LEAD FREE, PLASTIC, MO-119, SOIC-28 |

| 文件頁(yè)數(shù): | 25/44頁(yè) |

| 文件大?。?/td> | 542K |

| 代理商: | CY8C27443-24SXIT |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)當(dāng)前第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)

August 3, 2004

Document No. 38-12012 Rev. *I

25

CY8C27x43 Final Data Sheet

3. Electrical Specifications

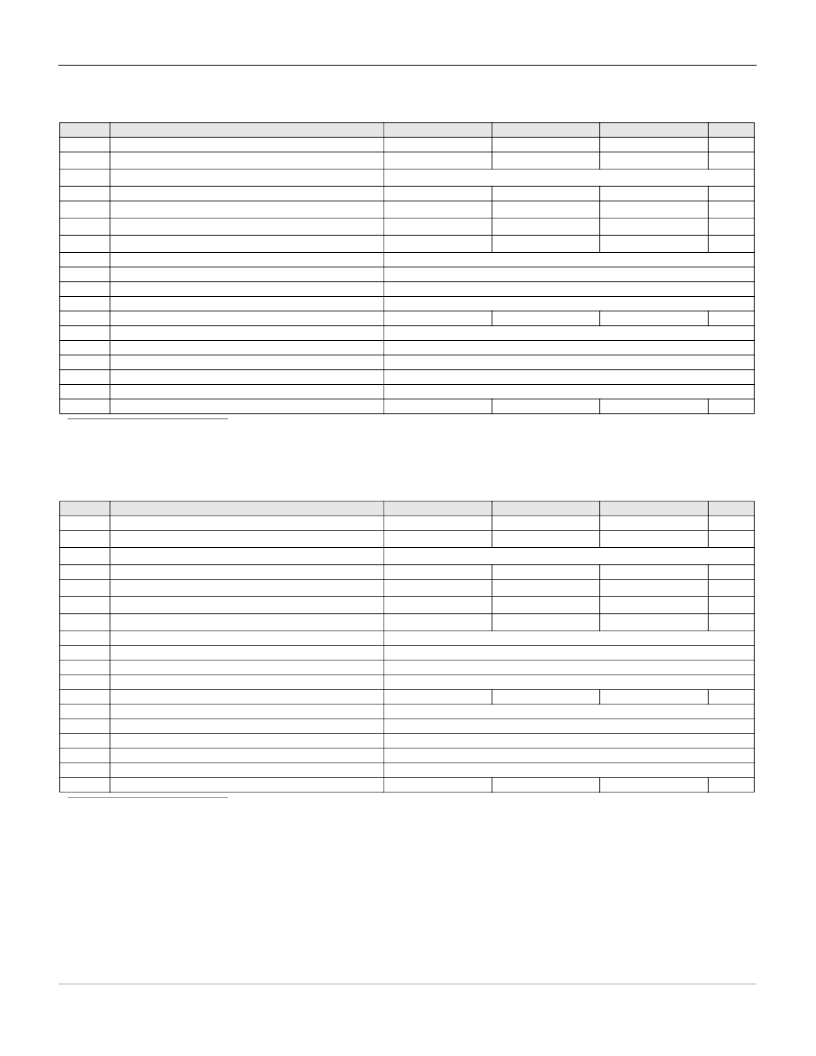

Table 3-13. Silicon Revision A – 3.3V DC Analog Reference Specifications

Symbol

BG

–

Description

Min

Typ

Max

Units

Bandgap Voltage Reference

AGND = Vdd/2

a

AGND = 2 x BandGap

a

AGND = P2[4] (P2[4] = Vdd/2)

AGND = BandGap

a

AGND = 1.6 x BandGap

a

AGND Block to Block Variation (AGND = Vdd/2)

a

RefHi = Vdd/2 + BandGap

RefHi = 3 x BandGap

RefHi = 2 x BandGap + P2[6] (P2[6] = 0.5V)

RefHi = P2[4] + BandGap (P2[4] = Vdd/2)

RefHi = P2[4] + P2[6] (P2[4] = Vdd/2, P2[6] = 0.5V)

RefHi = 3.2 x BandGap

RefLo = Vdd/2 - BandGap

RefLo = BandGap

RefLo = 2 x BandGap - P2[6] (P2[6] = 0.5V)

RefLo = P2[4] – BandGap (P2[4] = Vdd/2)

RefLo = P2[4]-P2[6] (P2[4] = Vdd/2, P2[6] = 0.5V)

1.274

Vdd/2 - 0.027

1.30

Vdd/2 - 0.003

1.326

Vdd/2 + 0.002

V

V

a. AGND tolerance includes the offsets of the local buffer in the PSoC block.

Note

See Application Note AN2012 “Adjusting PSoC Microcontroller Trims for Dual Voltage-Range Operation” for information on trimmng for operation at 3.3V.

–

Not Allowed

–

–

P2[4] - 0.008

BG - 0.009

P2[4] + 0.001

BG

P2[4] + 0.009

BG + 0.009

V

V

–

1.6 x BG - 0.018

1.6 x BG

1.6 x BG + 0.018

V

–

-0.034

0.000

0.034

mV

–

–

–

–

–

–

–

–

–

–

–

Not Allowed

Not Allowed

Not Allowed

Not Allowed

P2[4] + P2[6] - 0.075

Not Allowed

Not Allowed

Not Allowed

Not Allowed

Not Allowed

P2[4] - P2[6] - 0.048

P2[4] + P2[6] - 0.009

P2[4] + P2[6] + 0.057

V

P2[4] - P2[6] + 0.022

P2[4] - P2[6] + 0.092

V

Table 3-14. Silicon Revision B – 3.3V DC Analog Reference Specifications

Symbol

BG

–

Description

Min

Typ

Max

Units

Bandgap Voltage Reference

AGND = Vdd/2

a

AGND = 2 x BandGap

a

AGND = P2[4] (P2[4] = Vdd/2)

AGND = BandGap

a

AGND = 1.6 x BandGap

a

AGND Block to Block Variation (AGND = Vdd/2)

a

RefHi = Vdd/2 + BandGap

RefHi = 3 x BandGap

RefHi = 2 x BandGap + P2[6] (P2[6] = 0.5V)

RefHi = P2[4] + BandGap (P2[4] = Vdd/2)

RefHi = P2[4] + P2[6] (P2[4] = Vdd/2, P2[6] = 0.5V)

RefHi = 3.2 x BandGap

RefLo = Vdd/2 - BandGap

RefLo = BandGap

RefLo = 2 x BandGap - P2[6] (P2[6] = 0.5V)

RefLo = P2[4] – BandGap (P2[4] = Vdd/2)

RefLo = P2[4]-P2[6] (P2[4] = Vdd/2, P2[6] = 0.5V)

1.28

Vdd/2 - 0.027

1.30

Vdd/2

1.32

Vdd/2 + 0.005

V

V

a. AGND tolerance includes the offsets of the local buffer in the PSoC block.

Note

See Application Note AN2012 “Adjusting PSoC Microcontroller Trims for Dual Voltage-Range Operation” for information on trimmng for operation at 3.3V.

–

Not Allowed

–

–

P2[4] - 0.008

BG - 0.009

P2[4]

BG

P2[4] + 0.009

BG + 0.009

V

V

–

1.6 x BG - 0.018

1.6 x BG

1.6 x BG + 0.018

V

–

-0.034

0.000

0.034

mV

–

–

–

–

–

–

–

–

–

–

–

Not Allowed

Not Allowed

Not Allowed

Not Allowed

P2[4] + P2[6] - 0.06

Not Allowed

Not Allowed

Not Allowed

Not Allowed

Not Allowed

P2[4] - P2[6] - 0.048

P2[4] + P2[6] - 0.01

P2[4] + P2[6] + 0.057

V

P2[4] - P2[6] + 0.01

P2[4] - P2[6] + 0.048

V

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY8C27543-24AI | PSoC Mixed Signal Array |

| CY8C27143-24PXI | PSoC Mixed Signal Array |

| CY8C27243-24PVI | PSoC Mixed Signal Array |

| CY8C27243-24PVIT | PSoC Mixed Signal Array |

| CY8C27443-24PVI | PSoC Mixed Signal Array |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY8C2744324VXIT | 制造商:CYPRESS 功能描述:IC PSOC MIXED SIGNAL MICROCON |

| CY8C27443-24VXIT | 制造商:CYPRESS 功能描述:IC PSOC MIXED SIGNAL MICROCON |

| CY8C2754324AXI | 制造商:Cypress Semiconductor 功能描述: |

| CY8C27543-24AXI | 功能描述:可編程片上系統(tǒng) - PSoC IC MCU 16K FLSH 256B SRAM RoHS:否 制造商:Cypress Semiconductor 核心:8051 處理器系列:CY8C36 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:67 MHz 程序存儲(chǔ)器大小:32 KB 數(shù)據(jù) RAM 大小:4 KB 片上 ADC:Yes 工作電源電壓:0.5 V to 5.5 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:QFN-68 安裝風(fēng)格:SMD/SMT |

| CY8C27543-24AXIT | 功能描述:可編程片上系統(tǒng) - PSoC 16K FlSh 256B RAM IND RoHS:否 制造商:Cypress Semiconductor 核心:8051 處理器系列:CY8C36 數(shù)據(jù)總線寬度:8 bit 最大時(shí)鐘頻率:67 MHz 程序存儲(chǔ)器大小:32 KB 數(shù)據(jù) RAM 大小:4 KB 片上 ADC:Yes 工作電源電壓:0.5 V to 5.5 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:QFN-68 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。