- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379098 > CY8C27243-24PVIT (CYPRESS SEMICONDUCTOR CORP) PSoC Mixed Signal Array PDF資料下載

參數(shù)資料

| 型號: | CY8C27243-24PVIT |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | 外設及接口 |

| 英文描述: | PSoC Mixed Signal Array |

| 中文描述: | MULTIFUNCTION PERIPHERAL, PDSO20 |

| 封裝: | 0.210 INCH, LEAD FREE, SSOP-20 |

| 文件頁數(shù): | 24/44頁 |

| 文件大小: | 542K |

| 代理商: | CY8C27243-24PVIT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

August 3, 2004

Document No. 38-12012 Rev. *I

24

CY8C27x43 Final Data Sheet

3. Electrical Specifications

3.3.6

DC Analog Reference Specifications

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V

and -40

°

C

≤

T

A

≤

85

°

C, or 3.0V to 3.6V and -40

°

C

≤

T

A

≤

85

°

C, respectively. Typical parameters apply to 5V and 3.3V at 25

°

C and

are for design guidance only.

The guaranteed specifications are measured through the Analog Continuous Time PSoC blocks. The power levels for AGND refer to

the power of the Analog Continuous Time PSoC block. The power levels for RefHi and RefLo refer to the Analog Reference Control

register. The limits stated for AGND include the offset error of the AGND buffer local to the Analog Continuous Time PSoC block.

Reference control power is high.

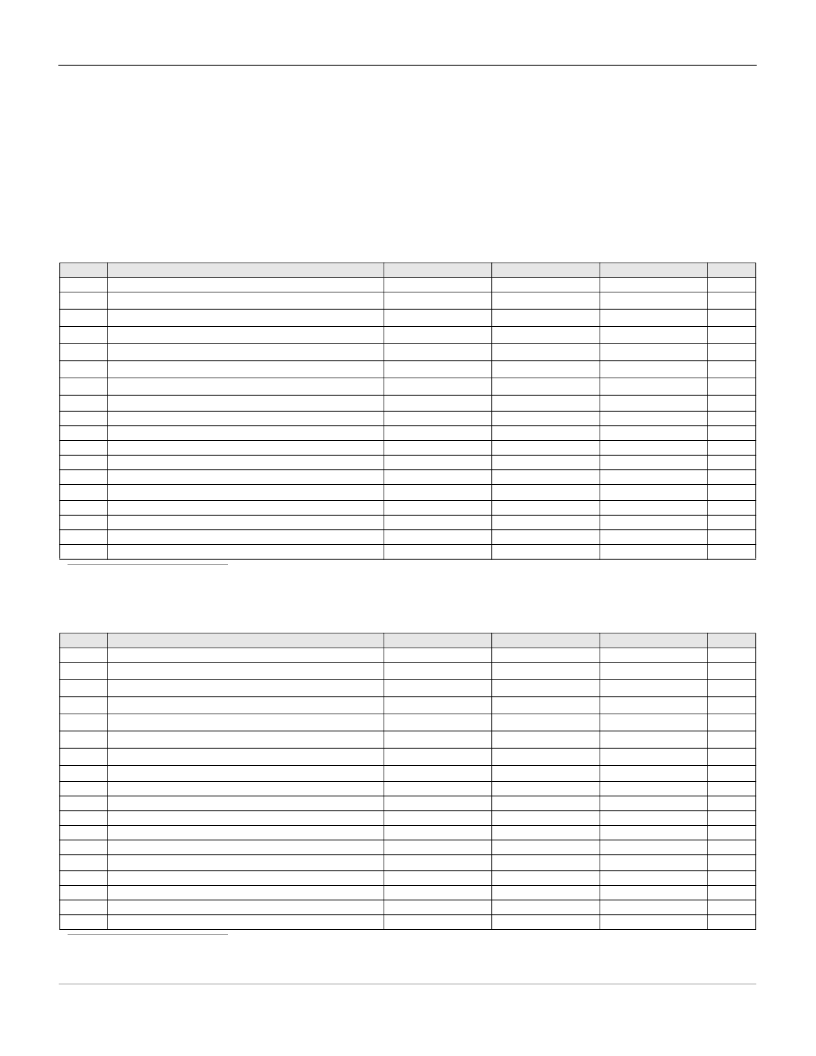

Table 3-11. Silicon Revision A – 5V DC Analog Reference Specifications

Symbol

BG

–

Description

Min

Typ

Max

Units

Bandgap Voltage Reference

AGND = Vdd/2

a

AGND = 2 x BandGap

a

AGND = P2[4] (P2[4] = Vdd/2)

a

AGND = BandGap

a

AGND = 1.6 x BandGap

a

AGND Block to Block Variation (AGND = Vdd/2)

a

RefHi = Vdd/2 + BandGap

1.274

Vdd/2 - 0.030

1.30

Vdd/2 - 0.004

1.326

Vdd/2 + 0.003

V

V

a. AGND tolerance includes the offsets of the local buffer in the PSoC block.

–

2 x BG - 0.043

2 x BG - 0.010

2 x BG + 0.024

V

–

P2[4] - 0.013

P2[4]

P2[4] + 0.014

V

–

BG - 0.009

BG

BG + 0.009

V

–

1.6 x BG - 0.018

1.6 x BG

1.6 x BG + 0.018

V

–

-0.034

0.000

0.034

V

–

Vdd

/2 + BG - 0.140

3 x BG - 0.112

2 x BG + P2[6] - 0.113

P2[4] + BG - 0.130

P2[4] + P2[6] - 0.133

3.2 x BG - 0.112

Vdd

/2 - BG - 0.051

BG - 0.082

2 x BG - P2[6] - 0.084

P2[4] - BG - 0.056

P2[4] - P2[6] - 0.057

Vdd

/2 + BG - 0.018

3 x BG - 0.018

2 x BG + P2[6] - 0.018

P2[4] + BG - 0.016

P2[4] + P2[6] - 0.016

3.2 x BG

Vdd

/2 - BG

+

0.024

BG + 0.023

2 x BG - P2[6] + 0.025

P2[4] - BG + 0.026

P2[4] - P2[6] + 0.026

Vdd

/2 + BG + 0.103

3 x BG + 0.076

2 x BG + P2[6] + 0.077

P2[4] + BG + 0.098

P2[4] + P2[6] + 0.100

3.2 x BG + 0.076

Vdd

/2 - BG + 0.098

BG + 0.129

2 x BG - P2[6] + 0.134

P2[4] - BG + 0.107

P2[4] - P2[6] + 0.110

V

–

–

–

–

–

–

RefHi = 3 x BandGap

RefHi = 2 x BandGap + P2[6] (P2[6] = 1.3V)

RefHi = P2[4] + BandGap (P2[4] = Vdd/2)

RefHi = P2[4] + P2[6] (P2[4] = Vdd/2, P2[6] = 1.3V)

RefHi = 3.2 x BandGap

RefLo = Vdd/2 – BandGap

V

V

V

V

V

V

–

–

–

–

RefLo = BandGap

RefLo = 2 x BandGap - P2[6] (P2[6] = 1.3V)

RefLo = P2[4] – BandGap (P2[4] = Vdd/2)

RefLo = P2[4]-P2[6] (P2[4] = Vdd/2, P2[6] = 1.3V)

V

V

V

V

Table 3-12. Silicon Revision B – 5V DC Analog Reference Specifications

Symbol

BG

–

Description

Min

Typ

Max

Units

Bandgap Voltage Reference

AGND = Vdd/2

a

AGND = 2 x BandGap

a

AGND = P2[4] (P2[4] = Vdd/2)

a

AGND = BandGap

a

AGND = 1.6 x BandGap

a

AGND Block to Block Variation (AGND = Vdd/2)

a

RefHi = Vdd/2 + BandGap

1.28

Vdd/2 - 0.030

1.30

Vdd/2

1.32

Vdd/2 + 0.007

V

V

a. AGND tolerance includes the offsets of the local buffer in the PSoC block.

–

2 x BG - 0.043

2 x BG

2 x BG + 0.024

V

–

P2[4] - 0.011

P2[4]

P2[4] + 0.011

V

–

BG - 0.009

BG

BG + 0.009

V

–

1.6 x BG - 0.018

1.6 x BG

1.6 x BG + 0.018

V

–

-0.034

0.000

0.034

V

–

Vdd

/2 + BG - 0.1

3 x BG - 0.06

2 x BG + P2[6] - 0.06

P2[4] + BG - 0.06

P2[4] + P2[6] - 0.06

3.2 x BG - 0.06

Vdd

/2 - BG - 0.051

BG - 0.06

2 x BG - P2[6] - 0.04

P2[4] - BG - 0.056

P2[4] - P2[6] - 0.056

Vdd

/2 + BG - 0.01

3 x BG - 0.01

2 x BG + P2[6] - 0.01

P2[4] + BG - 0.01

P2[4] + P2[6] - 0.01

3.2 x BG - 0.01

Vdd

/2 - BG

+

0.01

BG + 0.01

2 x BG - P2[6] + 0.01

P2[4] - BG + 0.01

P2[4] - P2[6] + 0.01

Vdd

/2 + BG + 0.1

3 x BG + 0.06

2 x BG + P2[6] + 0.06

P2[4] + BG + 0.06

P2[4] + P2[6] + 0.06

3.2 x BG + 0.06

Vdd

/2 - BG + 0.06

BG + 0.06

2 x BG - P2[6] + 0.04

P2[4] - BG + 0.056

P2[4] - P2[6] + 0.056

V

–

–

–

–

–

–

RefHi = 3 x BandGap

RefHi = 2 x BandGap + P2[6] (P2[6] = 1.3V)

RefHi = P2[4] + BandGap (P2[4] = Vdd/2)

RefHi = P2[4] + P2[6] (P2[4] = Vdd/2, P2[6] = 1.3V)

RefHi = 3.2 x BandGap

RefLo = Vdd/2 – BandGap

V

V

V

V

V

V

–

–

–

–

RefLo = BandGap

RefLo = 2 x BandGap - P2[6] (P2[6] = 1.3V)

RefLo = P2[4] – BandGap (P2[4] = Vdd/2)

RefLo = P2[4]-P2[6] (P2[4] = Vdd/2, P2[6] = 1.3V)

V

V

V

V

相關PDF資料 |

PDF描述 |

|---|---|

| CY8C27443-24PVI | PSoC Mixed Signal Array |

| CY8C27443-24PVIT | PSoC Mixed Signal Array |

| CY8C27443-24PXI | PSoC Mixed Signal Array |

| CY9C62256-70PC | 32K x 8 Magnetic Nonvolatile CMOS RAM |

| CY9C62256-70SC | 32K x 8 Magnetic Nonvolatile CMOS RAM |

相關代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY8C27243-24PVXI | 功能描述:可編程片上系統(tǒng) - PSoC IC MCU 16K FLSH 256B SRAM RoHS:否 制造商:Cypress Semiconductor 核心:8051 處理器系列:CY8C36 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:67 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:4 KB 片上 ADC:Yes 工作電源電壓:0.5 V to 5.5 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:QFN-68 安裝風格:SMD/SMT |

| CY8C27243-24PVXIT | 功能描述:可編程片上系統(tǒng) - PSoC 16K FlSh 256B RAM IND RoHS:否 制造商:Cypress Semiconductor 核心:8051 處理器系列:CY8C36 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:67 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:4 KB 片上 ADC:Yes 工作電源電壓:0.5 V to 5.5 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:QFN-68 安裝風格:SMD/SMT |

| CY8C27243-24SI | 制造商:Cypress Semiconductor 功能描述:PSOC Microcontroller 5.25V 20-Pin SOIC |

| CY8C2724324SXI | 制造商:Cypress Semiconductor 功能描述: |

| CY8C27243-24SXI | 功能描述:可編程片上系統(tǒng) - PSoC IC MCU 16K FLSH 256B SRAM RoHS:否 制造商:Cypress Semiconductor 核心:8051 處理器系列:CY8C36 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:67 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:4 KB 片上 ADC:Yes 工作電源電壓:0.5 V to 5.5 V 工作溫度范圍:- 40 C to + 85 C 封裝 / 箱體:QFN-68 安裝風格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復。