- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379096 > CY7C63803 (Cypress Semiconductor Corp.) enCoRe II Low-Speed USB Peripheral Controller(enCoRe II低速USB外設控制器) PDF資料下載

參數(shù)資料

| 型號: | CY7C63803 |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | enCoRe II Low-Speed USB Peripheral Controller(enCoRe II低速USB外設控制器) |

| 中文描述: | enCoRe II還低速USB外設控制器(enCoRe II還低速的USB外設控制器) |

| 文件頁數(shù): | 55/74頁 |

| 文件大?。?/td> | 1441K |

| 代理商: | CY7C63803 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁當前第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁

CY7C63310

CY7C638xx

Document 38-08035 Rev. *I

Page 55 of 74

21.4

Endpoint 1 and 2 Mode

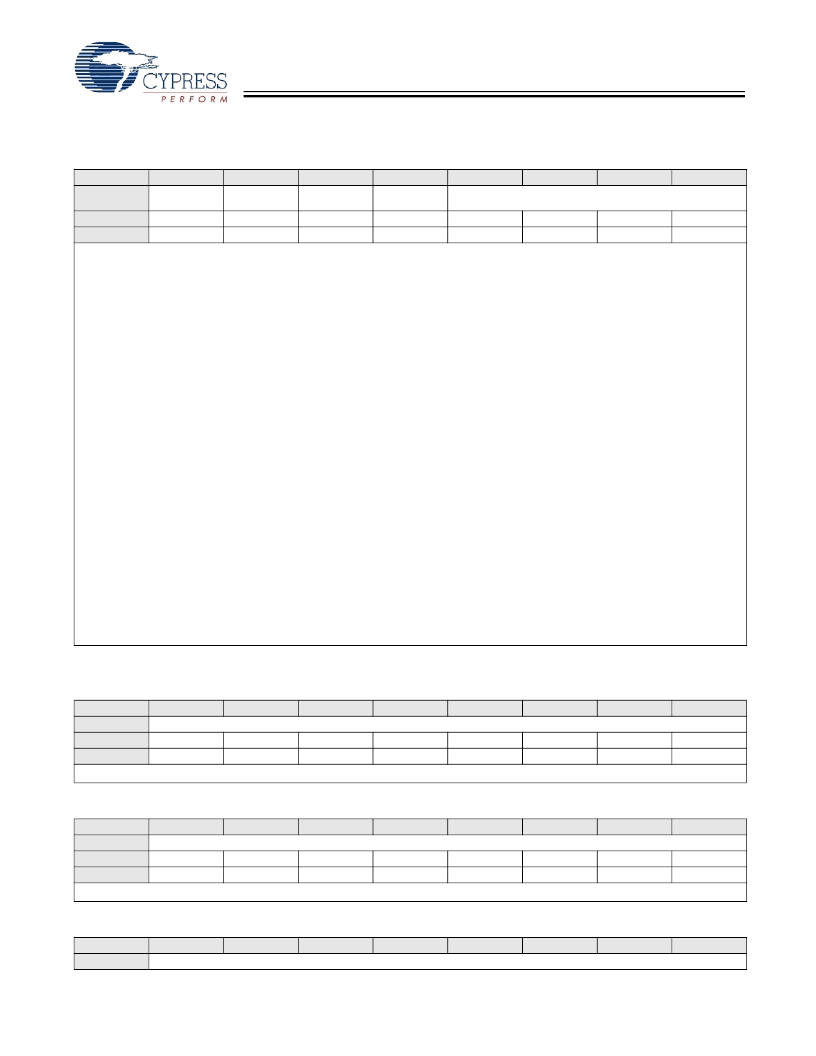

Table 21-4. Endpoint 1 and 2 Mode (EP1MODE – EP2MODE) [0x45, 0x46] [R/W]

Bit #

7

6

5

4

3

2

1

0

Field

Stall

Reserved

NAK Int Enable

ACK’d

Transaction

Mode[3:0]

Read/Write

R/W

R/W

R/W

R/C (Note 4)

R/W

R/W

R/W

R/W

Default

0

0

0

0

0

0

0

0

Bit 7:

Stall

When this bit is set the SIE will stall an OUT packet if the Mode Bits are set to ACK-OUT, and the SIE will stall an IN packet if

the mode bits are set to ACK-IN. This bit must be clear for all other modes

Bit 6:

Reserved

Bit 5:

NAK Int Enable

This bit when set causes an endpoint interrupt to be generated even when a transfer completes with a NAK. Unlike enCoRe,

enCoRe II family members do not generate an endpoint interrupt under these conditions unless this bit is set

0 = Disable interrupt on NAK’d transactions

1 = Enable interrupt on NAK’d transaction

Bit 4:

ACK’d Transaction

The ACK’d transaction bit is set whenever the SIE engages in a transaction to the register’s endpoint that completes with an

ACK packet.

This bit is cleared by any writes to the register

0 = The transaction does not complete with an ACK

1 = The transaction completes with an ACK

Bit [3:0]:

Mode [3:0]

The endpoint modes determine how the SIE responds to USB traffic that the host sends to the endpoint. The mode controls how the

USB SIE responds to traffic and how the USB SIE will change the mode of that endpoint as a result of host packets to the endpoint.

Note:

When the SIE writes to the EP1MODE or the EP2MODE register it blocks firmware writes to the EP2MODE or the EP1MODE

registers respectively (if both writes occur in the same clock cycle). This is because the design employs only one common ‘update’

signal for both EP1MODE and EP2MODE registers. Thus, when SIE writes to say EP1MODE register, the update signal is set and

this prevents firmware writes to EP2MODE register. SIE writes to the endpoint mode registers have higher priority than firmware

writes. This mode register write block situation can put the endpoints in incorrect modes. Firmware must read the EP1/2MODE regis-

ters immediately following a firmware write and rewrite if the value read is incorrect.

Table 21-5. Endpoint 0 Data (EP0DATA) [0x50-0x57] [R/W]

Bit #

7

6

5

4

3

2

1

0

Field

Endpoint 0 Data Buffer [7:0]

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Default

Unknown

Unknown

Unknown

Unknown

Unknown

Unknown

Unknown

Unknown

The Endpoint 0 buffer is comprised of 8 bytes located at address 0x50 to 0x57

Table 21-6. Endpoint 1 Data (EP1DATA) [0x58-0x5F] [R/W]

Bit #

7

6

5

4

3

2

1

0

Field

Endpoint 1 Data Buffer [7:0]

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Default

Unknown

Unknown

Unknown

Unknown

Unknown

Unknown

Unknown

Unknown

The Endpoint 1buffer is comprised of 8 bytes located at address 0x58 to 0x5F

Table 21-7. Endpoint 2 Data (EP2DATA) [0x60-0x67] [R/W]

Bit #

7

6

5

4

3

2

1

0

Field

Endpoint 2 Data Buffer [7:0]

相關PDF資料 |

PDF描述 |

|---|---|

| CY7C63310 | enCoRe II Low-Speed USB Peripheral Controller(enCoRe II低速USB外設控制器) |

| CY7C63801 | enCoRe II Low-Speed USB Peripheral Controller(enCoRe II低速USB外設控制器) |

| CY7C63823 | enCoRe II Low-Speed USB Peripheral Controller(enCoRe II低速USB外設控制器) |

| CY7C63813 | enCoRe II Low-Speed USB Peripheral Controller(enCoRe II低速USB外設控制器) |

| CY7C63833 | enCoRe II Low-Speed USB Peripheral Controller(enCoRe II低速USB外設控制器) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C638034-LQXC | 功能描述:IC USB CONTROLLER RoHS:是 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標準包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應商設備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| CY7C638034-SXC | 功能描述:IC USB CONTROLLERS RoHS:是 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標準包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應商設備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| CY7C638035-LQXC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C638035-SXC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C63803-LQXC | 功能描述:USB 接口集成電路 USB Peripheral Cntrl 8K/256 24-QFN RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

發(fā)布緊急采購,3分鐘左右您將得到回復。