- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379091 > CY7C375 (Cypress Semiconductor Corp.) UltraLogic 128-Macrocell Flash CPLD(超邏輯的128 宏單元閃速CPLD) PDF資料下載

參數(shù)資料

| 型號(hào): | CY7C375 |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | UltraLogic 128-Macrocell Flash CPLD(超邏輯的128 宏單元閃速CPLD) |

| 中文描述: | UltraLogic 128宏單元CPLD的閃光(超邏輯的128個(gè)宏單元閃速的CPLD) |

| 文件頁(yè)數(shù): | 1/1頁(yè) |

| 文件大小: | 48K |

| 代理商: | CY7C375 |

For new designs see CY7C375i

UltraLogic 128-Macrocell Flash CPLD

fax id: 6130

CY7C375

Cypress Semiconductor Corporation

3901 North First Street

San Jose

CA 95134

408-943-2600

September 1992 – Revised April 1998

Features

28 macrocells in eight logic blocks

28 I/O pins

6 dedicated inputs including 4 clock pins

Bus Hold capabilities on all I/Os and dedicated inputs

No hidden delays

High speed

—f

MAX

= 100 MHz

—t

PD

= 12 ns

—t

S

= 6 ns

—t

CO

= 7 ns

Electrically alterable FLASH technology

Available in 160-pin TQFP, CQFP, and PGA packages

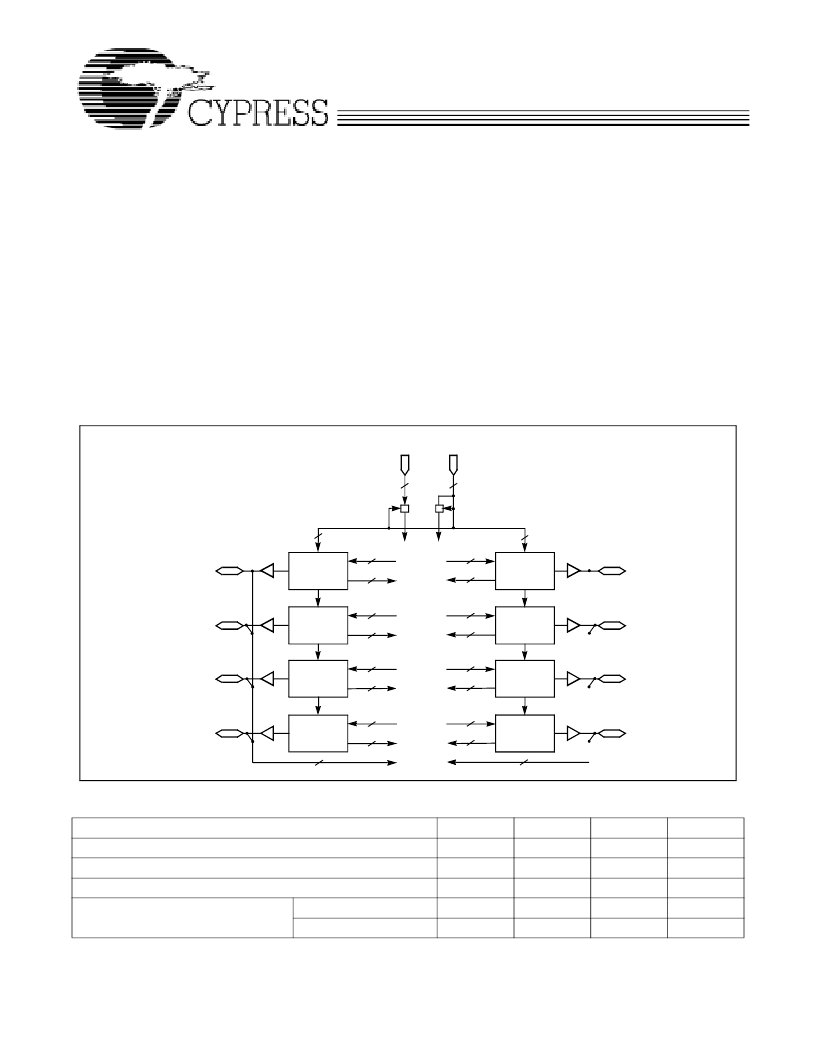

Functional Description

The CY7C375 is a Flash erasable Complex Programmable

Logic Device (CPLD) and is part of the F

LASH

370 family of

high-density, high-speed CPLDs. Like all members of the

F

LASH

370 family, the CY7C375 is designed to bring the ease

of use and high performance of the 22V10 to high-density

PLDs.

The 128 macrocells in the CY7C375 are divided between eight

logic blocks. Each logic block includes 16 macrocells, a 72 x

86 product term array, and an intelligent product term allocator.

The logic blocks in the F

LASH

370 architecture are connected

with an extremely fast and predictable routing resource—the

Programmable Interconnect Matrix (PIM). The PIM brings flex-

ibility, routability, speed, and a uniform delay to the intercon-

nect.

PIM

INPUT

MACROCELLS

CLOCK

INPUTS

INPUTS

LOGIC

BLOCK

B

LOGIC

BLOCK

G

4

4

36

16

16

36

LOGIC

BLOCK

A

LOGIC

BLOCK

H

36

16

16

36

16 I/Os

LOGIC

BLOCK

C

LOGIC

BLOCK

F

36

16

16

36

LOGIC

BLOCK

E

36

16

16

36

64

64

4

2

INPUT/CLOCK

MACROCELLS

Logic Block Diagram

I/O

0

I/O

15

I/O

16

I/O

31

I/O

32

I/O

47

I/O

48

I/O

63

I/O

112

I/O

127

I/O

96

I/O

111

I/O

80

I/O

95

I/O

64

I/O

79

LOGIC

BLOCK

D

16 I/Os

16 I/Os

16 I/Os

16 I/Os

16 I/Os

16 I/Os

16 I/Os

Selection Guide

7C375-100

7C375-83

7C375-66

7C375L-66

Maximum Propagation Delay, t

PD

(ns)

Minimum Set-Up, t

S

(ns)

Maximum Clock to Output, t

CO (ns)

Maximum Supply

Current, I

CC

(mA)

12

15

20

20

6

8

10

10

7

8

10

10

Commercial

330

300

300

150

Military/Industrial

370

370

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C402 | 64 x 5 Cascadable FIFO(64 x 5位級(jí)聯(lián)型先進(jìn)先出(FIFO)) |

| CY7C401 | 64 x 4 Cascadable FIFO(64 x 4 位級(jí)聯(lián)型先進(jìn)先出(FIFO)) |

| CY7C403 | 64 x 4 Cascadable FIFO(64 x 4 位級(jí)聯(lián)型先進(jìn)先出(FIFO)) |

| CY7C404 | 64 x 5 Cascadable FIFO(64 x 5位 級(jí)聯(lián)型先進(jìn)先出(FIFO)) |

| CY7C409A | 64 x 9 Cascadable FIFO(64 x 9位級(jí)聯(lián)型先進(jìn)先出(FIFO)) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C3751-66UMB | 制造商: 功能描述: 制造商:undefined 功能描述: |

| CY7C375I-125AC | 功能描述:IC CPLD 128 MACROCELL 160LQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - CPLD(復(fù)雜可編程邏輯器件) 系列:Ultralogic™ 標(biāo)準(zhǔn)包裝:40 系列:ispMACH® 4000C 可編程類型:系統(tǒng)內(nèi)可編程 最大延遲時(shí)間 tpd(1):5.0ns 電壓電源 - 內(nèi)部:1.65 V ~ 1.95 V 邏輯元件/邏輯塊數(shù)目:32 宏單元數(shù):512 門數(shù):- 輸入/輸出數(shù):128 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:176-LQFP 供應(yīng)商設(shè)備封裝:176-TQFP(24x24) 包裝:托盤(pán) |

| CY7C375I-66AC | 制造商:Cypress Semiconductor 功能描述:CPLD FLASH370i Family 3.2K Gates 128 Macro Cells CMOS Technology 5V 160-Pin TQFP |

| CY7C375I-66AI | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Cypress Semiconductor 功能描述: |

| CY7C375IL-66AC | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Cypress Semiconductor 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。