- 您現在的位置:買賣IC網 > PDF目錄379087 > CY7C1522AV18-200BZXC (CYPRESS SEMICONDUCTOR CORP) 72-Mbit DDR-II SIO SRAM 2-Word Burst Architecture PDF資料下載

參數資料

| 型號: | CY7C1522AV18-200BZXC |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | DRAM |

| 英文描述: | 72-Mbit DDR-II SIO SRAM 2-Word Burst Architecture |

| 中文描述: | 8M X 8 DDR SRAM, 0.45 ns, PBGA165 |

| 封裝: | 15 X 17 MM, 1.40 MM HEIGHT, LEAD FREE, MO-216, FBGA-165 |

| 文件頁數: | 9/28頁 |

| 文件大小: | 1133K |

| 代理商: | CY7C1522AV18-200BZXC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

PRELIMINARY

CY7C1522AV18

CY7C1529AV18

CY7C1523AV18

CY7C1524AV18

Document #: 001-06981 Rev. *B

Page 9 of 28

DLL

These chips utilize a Delay Lock Loop (DLL) that is designed

to function between 80 MHz and the specified maximum clock

frequency. During power-up, when the DOFF is tied HIGH, the

DLL gets locked after 1024 cycles of stable clock. The DLL can

also be reset by slowing or stopping the input clock K and K

for a minimum of 30 ns. However, it is not necessary for the

DLL to be specifically reset in order to lock the DLL to the

desired frequency. The DLL will automatically lock 1024 clock

cycles after a stable clock is presented.the DLL may be

disabled by applying ground to the DOFF pin. When the DLL

is turned off, the device will behave in DDR-I mode (with one

cycle latency and a longer access time). For information refer

to

the

application

note

QDRII/DDRII”.

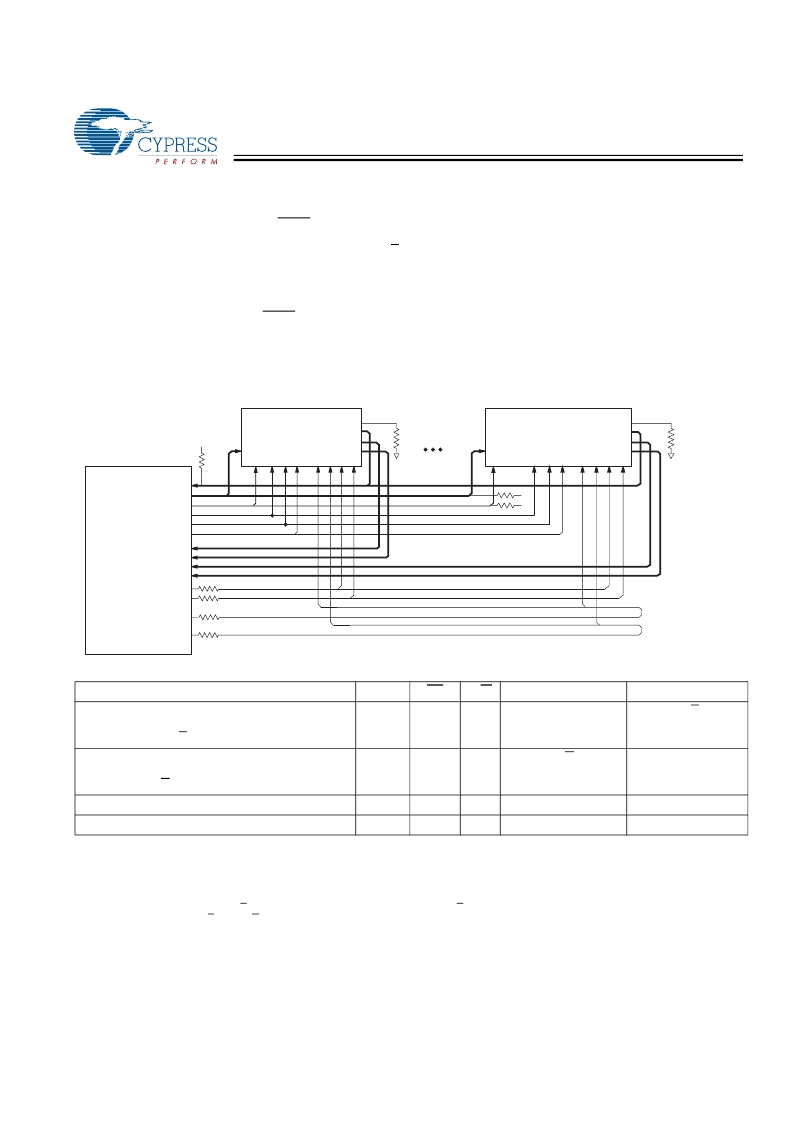

Application Example

[2]

“DLL

Considerations

in

Truth Table

[3, 4, 5, 6, 7, 8]

Operation

K

LD

L

R/W

L

DQ

DQ

Write Cycle:

Load address; wait one cycle; input write data on

consecutive K and K rising edges.

Read Cycle:

Load address; wait one and a half cycle; read data

on consecutive C and C rising edges.

NOP: No Operation

Standby: Clock Stopped

L-H

D(A + 0) at K(t + 1)

↑

D(A + 1) at K(t + 1)

↑

L-H

L

H

Q(A + 0) at C(t + 1)

↑

Q(A + 1) at C(t + 2)

↑

L-H

H

X

X

X

High-Z

Previous State

High-Z

Previous State

Stopped

Notes:

2. The above application shows four DDR-II SIO being used.

3. X = “Don't Care,” H = Logic HIGH, L = Logic LOW,

↑

represents rising edge.

4. Device will power-up deselected and the outputs in a tri-state condition.

5. “A” represents address location latched by the devices when transaction was initiated. A + 0, A + 1 represents the internal address sequence in the burst.

6. “t” represents the cycle at which a Read/Write operation is started. t+1, t + 2 and t +3 are the first, second and third clock cycles succeeding the “t” clock cycle.

7. Data inputs are registered at K and K rising edges. Data outputs are delivered on C and C rising edges, except when in single clock mode.

8. It is recommended that K = K and C = C = HIGH when clock is stopped. This is not essential, but permits most rapid restart by overcoming transmission line

charging symmetrically.

LD

#

#

#

#

B

W

#

#

Vt = V

REF

C C#

CQ

CQ#

K#

ZQ

Q

D

K

C

C# K

BUS

MASTER

(CPU

or

ASIC)

SRAM 1

SRAM 4

DATA IN

DATA OUT

Address

LD#

R/W#

BWS#

SRAM 1 Input CQ

SRAM 1 Input CQ#

SRAM 4 Input CQ

SRAM 4 Input CQ#

Source K

Source K#

Delayed K

Delayed K#

R = 50

Ohms

R = 250

Ohms

CQ

CQ#

K#

ZQ

Q

LD

R/W

B

W

S

LD

#

R/W

#

Vt

Vt

Vt

R

R

R

A

A

D

R = 250

Ohms

B

W

S

#

[+] Feedback

相關PDF資料 |

PDF描述 |

|---|---|

| CY7C1522AV18-200BZXI | 72-Mbit DDR-II SIO SRAM 2-Word Burst Architecture |

| CY7C1522AV18-250BZC | 72-Mbit DDR-II SIO SRAM 2-Word Burst Architecture |

| CY7C1522AV18-250BZI | 72-Mbit DDR-II SIO SRAM 2-Word Burst Architecture |

| CY7C1522AV18-250BZXC | 72-Mbit DDR-II SIO SRAM 2-Word Burst Architecture |

| CY7C1522AV18-250BZXI | 72-Mbit DDR-II SIO SRAM 2-Word Burst Architecture |

相關代理商/技術參數 |

參數描述 |

|---|---|

| CY7C1523AV18-200BZC | 功能描述:靜態(tài)隨機存取存儲器 4M x 18 1.8V DDR II SIO 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1523AV18-250BZC | 功能描述:靜態(tài)隨機存取存儲器 4M x 18 1.8V DDR II SIO 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1523JV18-300BZXC | 功能描述:靜態(tài)隨機存取存儲器 4Mbx18 72Mb 1.7-1.9V 300 MHz 2 WORD BURST RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1523KV18-250BZ | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1523KV18-250BZXC | 功能描述:靜態(tài)隨機存取存儲器 72MB (4Mx18) 1.8v 250MHz DDR II 靜態(tài)隨機存取存儲器 RoHS:否 制造商:Cypress Semiconductor 存儲容量:16 Mbit 組織:1 M x 16 訪問時間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復。