- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379088 > CY7C1520V18-300BZXC (CYPRESS SEMICONDUCTOR CORP) 72-Mbit DDR-II SRAM 2-Word Burst Architecture PDF資料下載

參數(shù)資料

| 型號(hào): | CY7C1520V18-300BZXC |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | DRAM |

| 英文描述: | 72-Mbit DDR-II SRAM 2-Word Burst Architecture |

| 中文描述: | 2M X 36 DDR SRAM, 0.45 ns, PBGA165 |

| 封裝: | 15 X 17 MM, 1.40 MM HEIGHT, LEAD FREE, MO-216, FBGA-165 |

| 文件頁(yè)數(shù): | 10/28頁(yè) |

| 文件大小: | 457K |

| 代理商: | CY7C1520V18-300BZXC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)

CY7C1516V18

CY7C1527V18

CY7C1518V18

CY7C1520V18

Document #: 38-05563 Rev. *D

Page 10 of 28

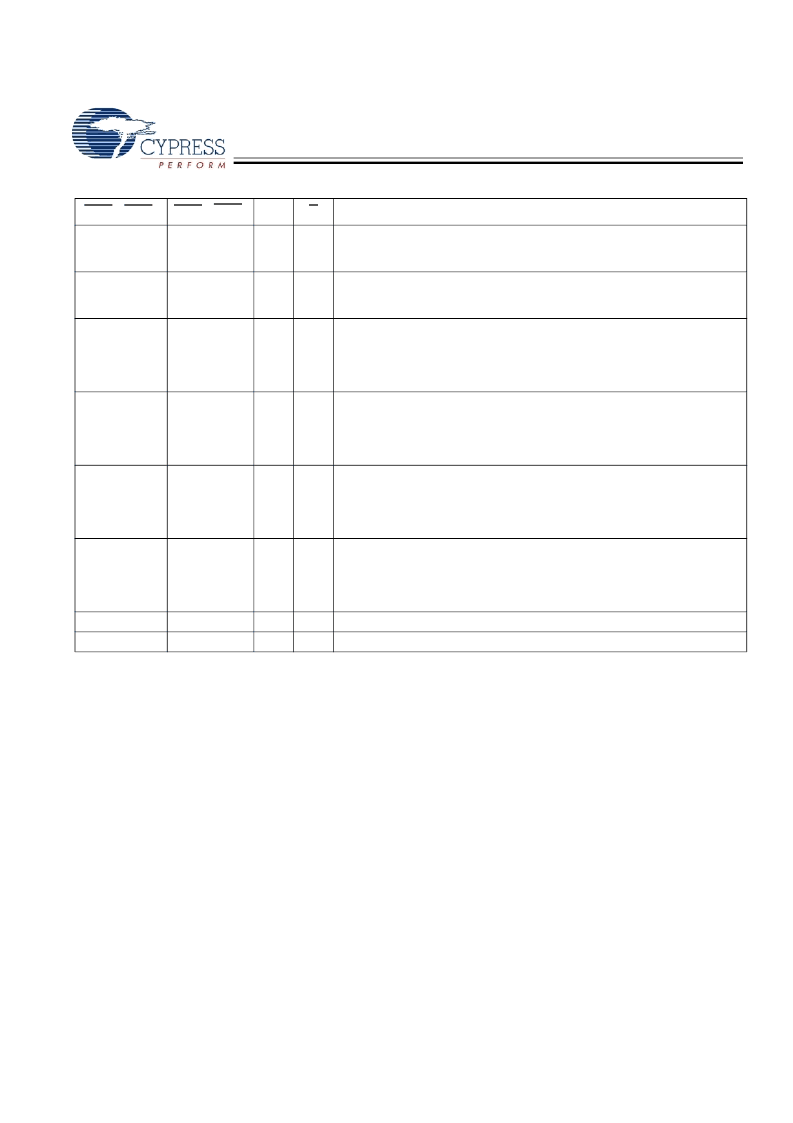

Write Cycle Descriptions

(CY7C1516V18 and CY7C1518V18)

[3, 9]

BWS

0

, NWS

0

L

BWS

1

, NWS

1

L

K

K

Comments

L-H

–

During the Data portion of a Write sequence

:

CY7C1516V18

both nibbles (D

[7:0]

) are written into the device,

CY7C1518V18

both bytes (D

[17:0]

) are written into the device.

During the Data portion of a Write sequence

:

CY7C1516V18

both nibbles (D

[7:0]

) are written into the device,

CY7C1518V18

both bytes (D

[17:0]

) are written into the device.

During the Data portion of a Write sequence

:

CY7C1516V18

only the lower nibble (D

[3:0]

) is written into the device. D

[7:4]

will remain unaltered,

CY7C1518V18

only the lower byte (D

[8:0]

) is written into the device. D

[17:9]

will remain unaltered.

During the Data portion of a Write sequence

:

CY7C1516V18

only the lower nibble (D

[3:0]

) is written into the device. D

[7:4]

will remain unaltered,

CY7C1518V18

only the lower byte (D

[8:0]

) is written into the device. D

[17:9]

will remain unaltered.

During the Data portion of a Write sequence

:

CY7C1516V18

only the upper nibble (D

[7:4]

) is written into the device. D

[3:0]

will remain unaltered,

CY7C1518V18

only the upper byte (D

[17:9]

) is written into the device. D

[8:0]

will remain unaltered.

During the Data portion of a Write sequence

:

CY7C1516V18

only the upper nibble (D

[7:4]

) is written into the device. D

[3:0]

will remain unaltered,

CY7C1518V18

only the upper byte (D

[17:9]

) is written into the device. D

[8:0]

will remain unaltered.

No data is written into the devices during this portion of a Write operation.

No data is written into the devices during this portion of a Write operation.

L

L

–

L-H

L

H

L-H

–

L

H

–

L-H

H

L

L-H

–

H

L

–

L-H

H

H

H

H

L-H

–

–

L-H

[+] Feedback

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C1520V18-300BZXI | 72-Mbit DDR-II SRAM 2-Word Burst Architecture |

| CY7C1527V18 | 72-Mbit DDR-II SRAM 2-Word Burst Architecture |

| CY7C1527V18-167BZC | 72-Mbit DDR-II SRAM 2-Word Burst Architecture |

| CY7C1527V18-167BZI | 72-Mbit DDR-II SRAM 2-Word Burst Architecture |

| CY7C1527V18-167BZXC | 72-Mbit DDR-II SRAM 2-Word Burst Architecture |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C1520XC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1520YC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1520ZC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1523AV18-200BZC | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 4M x 18 1.8V DDR II SIO 靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問(wèn)時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C1523AV18-250BZC | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 4M x 18 1.8V DDR II SIO 靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問(wèn)時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。