- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379066 > CY7C1370C (Cypress Semiconductor Corp.) 512K x 36/1M x 18 Pipelined SRAM with NoBL Architecture PDF資料下載

參數(shù)資料

| 型號: | CY7C1370C |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | 512K x 36/1M x 18 Pipelined SRAM with NoBL Architecture |

| 中文描述: | 為512k × 36/1M × 18流水線的SRAM架構(gòu)的總線延遲 |

| 文件頁數(shù): | 2/27頁 |

| 文件大?。?/td> | 704K |

| 代理商: | CY7C1370C |

第1頁當前第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁

CY7C1370C

CY7C1372C

Document #: 38-05233 Rev. *D

Page 2 of 27

A0, A1, A

C

MODE

BW

a

BW

b

WE

CE1

CE2

CE3

OE

READ LOGIC

DQs

DQP

a

DQP

b

D

A

T

A

S

T

E

E

R

I

N

G

O

U

T

P

U

T

B

U

F

F

E

R

S

ARRAY

E

E

INPUT

REGISTER 0

ADDRESS

REGISTER 0

WRITE ADDRESS

REGISTER 1

WRITE ADDRESS

REGISTER 2

WRITE REGISTRY

AND DATA COHERENCY

CONTROL LOGIC

BURST

LOGIC

A0'

A1'

D1

D0

Q1

Q0

A0

A1

C

ADV/LD

ADV/LD

E

INPUT

REGISTER 1

S

E

N

S

E

A

M

P

S

O

U

T

P

U

T

R

E

G

I

S

T

E

R

S

E

CLK

CEN

WRITE

DRIVERS

ZZ

Sleep

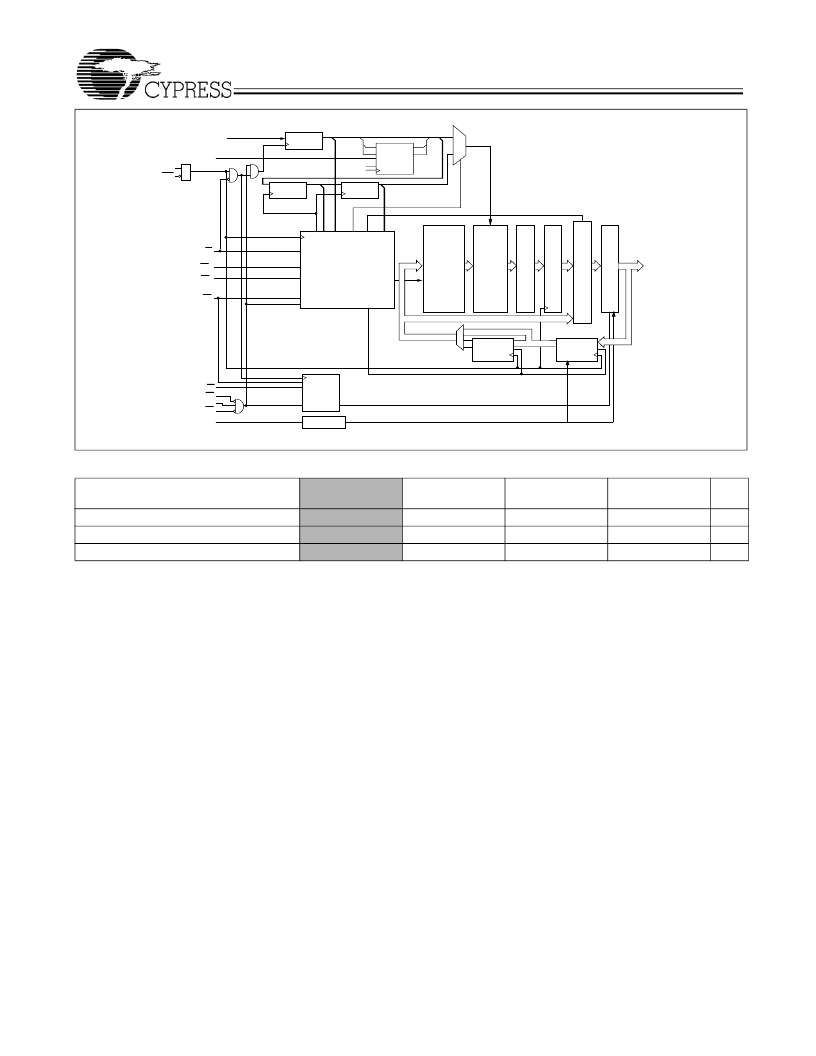

Logic Block Diagram-CY7C1372C (1M x 18)

Selection Guide

CY7C1370C-250

CY7C1372C-250

2.6

350

70

CY7C1370C-225

CY7C1372C-225

2.8

325

70

CY7C1370C-200

CY7C1372C-200

3.0

300

70

CY7C1370C-167

CY7C1372C-167

3.4

275

70

Unit

ns

mA

mA

Maximum Access Time

Maximum Operating Current

Maximum CMOS Standby Current

Shaded areas contain advance information. Please contact your local Cypress sales representative for availability of these parts.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C1372C-167BGC | 512K x 36/1M x 18 Pipelined SRAM with NoBL Architecture |

| CY7C1372C-167BGI | 512K x 36/1M x 18 Pipelined SRAM with NoBL Architecture |

| CY7C1372C-167BZC | 512K x 36/1M x 18 Pipelined SRAM with NoBL Architecture |

| CY7C1372C-167BZI | 512K x 36/1M x 18 Pipelined SRAM with NoBL Architecture |

| CY7C1372C-200AC | 512K x 36/1M x 18 Pipelined SRAM with NoBL Architecture |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C1370C-133BZC | 制造商:Cypress Semiconductor 功能描述:16MB (512KX36) 3.3V NOBL-PIPE SRAM - Bulk |

| CY7C1370C-167AI | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1370C-167BGI | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1370C167BZC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1370C-200BGC | 制造商:Cypress Semiconductor 功能描述:SRAM Chip Sync Single 3.3V 18M-Bit 512K x 36 3ns 119-Pin BGA |

發(fā)布緊急采購,3分鐘左右您將得到回復。