- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄379067 > CY7C1370C-225AI (CYPRESS SEMICONDUCTOR CORP) 512K x 36/1M x 18 Pipelined SRAM with NoBL Architecture PDF資料下載

參數(shù)資料

| 型號(hào): | CY7C1370C-225AI |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類(lèi): | DRAM |

| 英文描述: | 512K x 36/1M x 18 Pipelined SRAM with NoBL Architecture |

| 中文描述: | 512K X 36 ZBT SRAM, 2.8 ns, PQFP100 |

| 封裝: | 14 X 20 MM, 1.40 MM HEIGHT, PLASTIC, TQFP-100 |

| 文件頁(yè)數(shù): | 20/27頁(yè) |

| 文件大小: | 704K |

| 代理商: | CY7C1370C-225AI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)當(dāng)前第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)

CY7C1370C

CY7C1372C

Document #: 38-05233 Rev. *D

Page 20 of 27

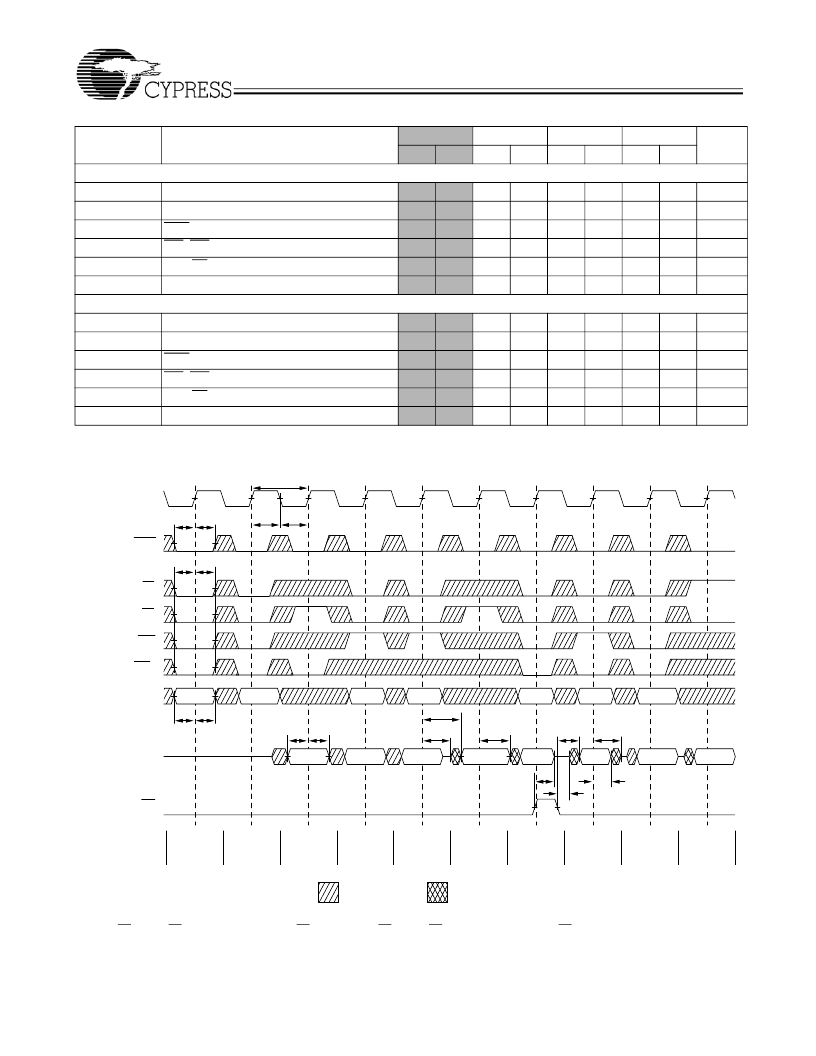

Set-up Times

t

AS

t

DS

t

CENS

t

WES

t

ALS

t

CES

Hold Times

t

AH

t

DH

t

CENH

t

WEH

t

ALH

t

CEH

Address Set-up Before CLK Rise

Data Input Set-up Before CLK Rise

1.2

1.2

1.2

1.2

1.2

1.2

1.4

1.4

1.4

1.4

1.4

1.4

1.4

1.4

1.4

1.4

1.4

1.4

1.5

1.5

1.5

1.5

1.5

1.5

ns

ns

ns

ns

ns

ns

CEN Set-up Before CLK Rise

WE, BW

x

Set-up Before CLK Rise

ADV/LD Set-up Before CLK Rise

Chip Select Set-up

Address Hold After CLK Rise

Data Input Hold After CLK Rise

0.3

0.3

0.3

0.3

0.3

0.3

0.4

0.4

0.4

0.4

0.4

0.4

0.4

0.4

0.4

0.4

0.4

0.4

0.5

0.5

0.5

0.5

0.5

0.5

ns

ns

ns

ns

ns

ns

CEN Hold After CLK Rise

WE, BW

x

Hold After CLK Rise

ADV/LD Hold after CLK Rise

Chip Select Hold After CLK Rise

Switching Characteristics

Over the Operating Range

[ 21, 22]

(continued)

Parameter

Description

-250

-225

-200

-167

Unit

Min.

Max.

Min.

Max.

Min.

Max.

Min.

Max.

Switching Waveforms

Read/Write/Timing

[23,24,25]

Notes:

23.For this waveform ZZ is tied low.

24.When CE is LOW, CE

is LOW, CE

is HIGH and CE

is LOW. When CE is HIGH,CE

is HIGH or CE

is LOW or CE

is HIGH.

25.Order of the Burst sequence is determined by the status of the MODE (0=Linear, 1=Interleaved).Burst operations are optional.

WRITE

D(A1)

1

2

3

4

5

6

7

8

9

CLK

tCYC

t

CL

t

CH

10

CE

t

CEH

t

CES

WE

CEN

t

CENH

t

CENS

BW

x

ADV/LD

t

AH

t

AS

ADDRESS

A1

A2

A3

A4

A5

A6

A7

t

DH

t

DS

Data

In-Out (DQ)

t

CLZ

D(A1)

D(A2)

D(A5)

Q(A4)

Q(A3)

D(A2+1)

t

DOH

t

CHZ

t

CO

WRITE

D(A2)

BURST

WRITE

D(A2+1)

READ

Q(A3)

READ

Q(A4)

BURST

READ

Q(A4+1)

WRITE

D(A5)

READ

Q(A6)

WRITE

D(A7)

DESELECT

OE

t

OEV

t

OELZ

t

OEHZ

t

DOH

DON’T CARE

UNDEFINED

Q(A6)

Q(A4+1)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C1370C-225BGC | 512K x 36/1M x 18 Pipelined SRAM with NoBL Architecture |

| CY7C1370C-225BGI | 512K x 36/1M x 18 Pipelined SRAM with NoBL Architecture |

| CY7C1370C-225BZI | 512K x 36/1M x 18 Pipelined SRAM with NoBL Architecture |

| CY7C1370C-250AC | 512K x 36/1M x 18 Pipelined SRAM with NoBL Architecture |

| CY7C1370C-250AI | 512K x 36/1M x 18 Pipelined SRAM with NoBL Architecture |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C1370CV25-133AC | 制造商:Cypress Semiconductor 功能描述:16MB (512KX36) 2.5V NOBL-PIPE SRAM - Bulk |

| CY7C1370CV25-167AC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1370CV25167BZC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1370CV25-167BZI | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1370D-167AXC | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 512Kx36 3.3V NoBL Sync PL 靜態(tài)隨機(jī)存取存儲(chǔ)器 COM RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問(wèn)時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。