- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359518 > CY7C1360 (Cypress Semiconductor Corp.) Plastic Connector Backshell; Enclosure Material:Plastic; Enclosure Color:Beige; Features:Compatible with 101XX-6000EC Mini D Ribbon; Leaded Process Compatible:No; No. of Positions:36; Peak Reflow Compatible (260 C):No RoHS Compliant: No PDF資料下載

參數(shù)資料

| 型號(hào): | CY7C1360 |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | Plastic Connector Backshell; Enclosure Material:Plastic; Enclosure Color:Beige; Features:Compatible with 101XX-6000EC Mini D Ribbon; Leaded Process Compatible:No; No. of Positions:36; Peak Reflow Compatible (260 C):No RoHS Compliant: No |

| 中文描述: | 9兆位(256 × 36/512K × 18)流水線的SRAM |

| 文件頁(yè)數(shù): | 25/34頁(yè) |

| 文件大?。?/td> | 895K |

| 代理商: | CY7C1360 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)當(dāng)前第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)

CY7C1360B

CY7C1362B

Document #: 38-05291 Rev. *C

Page 25 of 34

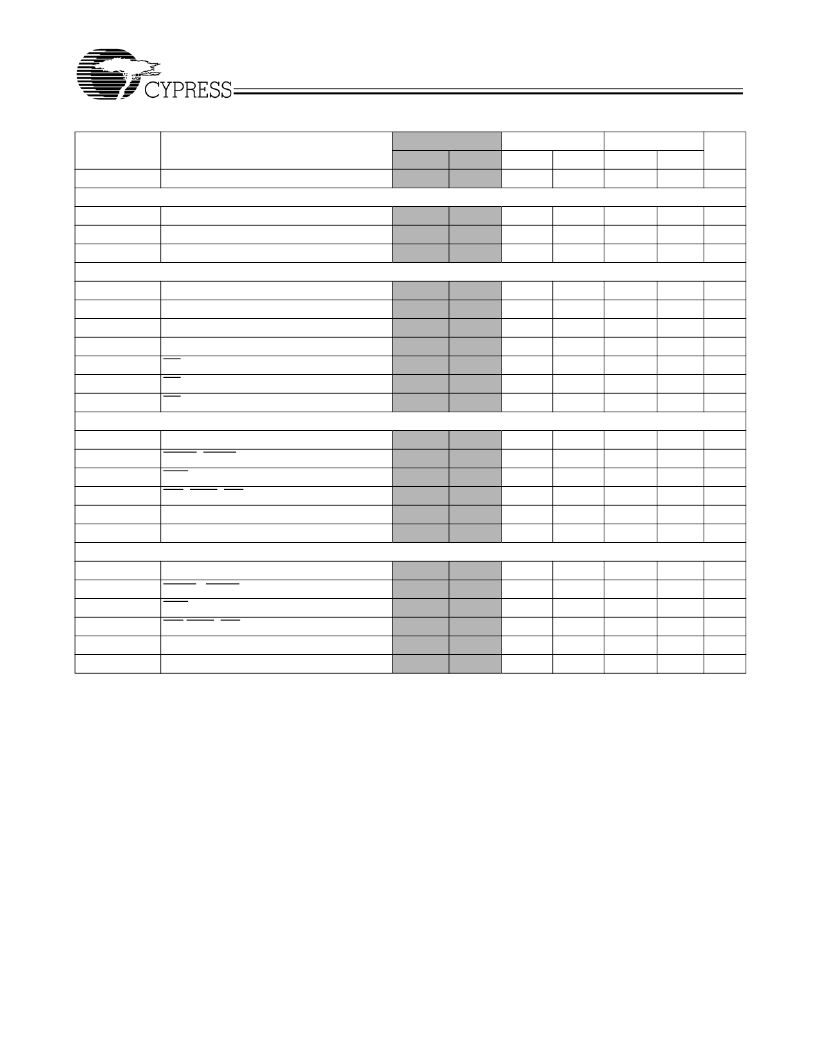

Switching Characteristics

Over the Operating Range

[16, 17]

Parameter

t

POWER

Clock

t

CYC

t

CH

t

CL

Output Times

t

CO

t

DOH

t

CLZ

t

CHZ

t

OEV

t

OELZ

t

OEHZ

Set-up Times

t

AS

t

ADS

t

ADVS

t

WES

t

DS

t

CES

Hold Times

t

AH

t

ADH

t

ADVH

t

WEH

t

DH

t

CEH

Shaded areas contain advance information.

Description

225 MHz

Min.

1

200 MHz

Min.

1

166 MHz

Min.

1

Unit

ms

Max

Max

Max

V

DD

(Typical) to the First Access

[18]

Clock Cycle Time

Clock HIGH

Clock LOW

4.4

1.8

1.8

5.0

2.0

2.0

6.0

2.4

2.4

ns

ns

ns

Data Output Valid after CLK Rise

Data Output Hold after CLK Rise

Clock to Low-Z

[19, 20, 21]

Clock to High-Z

[19, 20, 21]

OE LOW to Output Valid

OE LOW to Output Low-Z

[19, 20, 21]

OE HIGH to Output High-Z

[19, 20, 21]

2.8

3.0

3.5

ns

ns

ns

ns

ns

ns

ns

1.25

1.25

1.25

1.25

1.25

1.25

1.25

1.25

1.25

2.8

2.8

3.0

3.0

3.5

3.5

0

0

0

2.8

3.0

3.5

Address Set-up before CLK Rise

ADSC, ADSP Set-up before CLK Rise

ADV Set-up before CLK Rise

GW, BWE, BW

X

Set-up before CLK Rise

Data Input Set-up before CLK Rise

Chip Enable Set-Up before CLK Rise

1.4

1.4

1.4

1.4

1.4

1.4

1.5

1.5

1.5

1.5

1.5

1.5

1.5

1.5

1.5

1.5

1.5

1.5

ns

ns

ns

ns

ns

ns

Address Hold after CLK Rise

ADSP , ADSC Hold after CLK Rise

ADV Hold after CLK Rise

GW,BWE, BW

X

Hold after CLK Rise

Data Input Hold after CLK Rise

Chip Enable Hold after CLK Rise

0.4

0.4

0.4

0.4

0.4

0.4

0.5

0.5

0.5

0.5

0.5

0.5

0.5

0.5

0.5

0.5

0.5

0.5

ns

ns

ns

ns

ns

ns

Notes:

16.Timing reference level is 1.5V when V

= 3.3V and is 1.25V when V

DDQ

= 2.5V.

17.Test conditions shown in (a) of AC Test Loads unless otherwise noted.

18.This part has a voltage regulator internally; t

POWER

is the time that the power needs to be supplied above V

DD

(minimum) initially before a Read or Write operation

can be initiated.

19.t

, t

,t

, and t

are specified with AC test conditions shown in part (b) of AC Test Loads. Transition is measured ± 200 mV from steady-state voltage.

20.At any given voltage and temperature, t

is less than t

and t

is less than t

to eliminate bus contention between SRAMs when sharing the same

data bus. These specifications do not imply a bus contention condition, but reflect parameters guaranteed over worst case user conditions. Device is designed

to achieve High-Z prior to Low-Z under the same system conditions

21.This parameter is sampled and not 100% tested.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C1360B | BACKSHELL, MDR, 36WAY, SCREW; For use with:Mini D Ribbon Connectors; Material:Glass Reinforced Polyester (PBT); Colour:Black; Connector type:Backshell; Flammability rating:UL94V-0; Temp, op. max:85(degree C); Temp, op. min:-20(degree RoHS Compliant: Yes |

| CY7C1360B-225AI | BACKSHELL, MDR, 36WAY, METAL; For use with:Mini D Ribbon 101XX-6000 EC Plug Connectors; Material:Aluminum; Colour:Nickel; Connector type:Backshell; Ways, No. of:36 RoHS Compliant: Yes |

| CY7C1360B-225AJC | BACKSHELL, MDR, 36WAY, METAL; For use with:Mini D Ribbon 101XX-6000 EC Plug Connectors; Material:Aluminum; Colour:Steel; Connector type:Backshell; Ways, No. of:36 RoHS Compliant: Yes |

| CY7C1360B-225BGI | Plastic Connector Backshell; No. of Positions:40 RoHS Compliant: Yes |

| CY7C43646AV-10AC | 3.3V 1K 4K 16K x 36 x 18 x 2 Tri Bus FIFO |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C1360 WAF | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1360-166AJXCKJ | 制造商:Cypress Semiconductor 功能描述: |

| CY7C13601CC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C13607XC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1360A1-150AJC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。