- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄378497 > CY7C1176V18-300BZI (CYPRESS SEMICONDUCTOR CORP) 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.5 Cycle Read Latency) PDF資料下載

參數(shù)資料

| 型號(hào): | CY7C1176V18-300BZI |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類(lèi): | DRAM |

| 英文描述: | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.5 Cycle Read Latency) |

| 中文描述: | 2M X 9 QDR SRAM, 0.45 ns, PBGA165 |

| 封裝: | 13 X 15 MM, 1.40 MM HEIGHT, MO-216, FPBGA-165 |

| 文件頁(yè)數(shù): | 6/29頁(yè) |

| 文件大小: | 956K |

| 代理商: | CY7C1176V18-300BZI |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)

CY7C1161V18

CY7C1176V18

CY7C1163V18

CY7C1165V18

Document Number: 001-06582 Rev. *C

Page 6 of 29

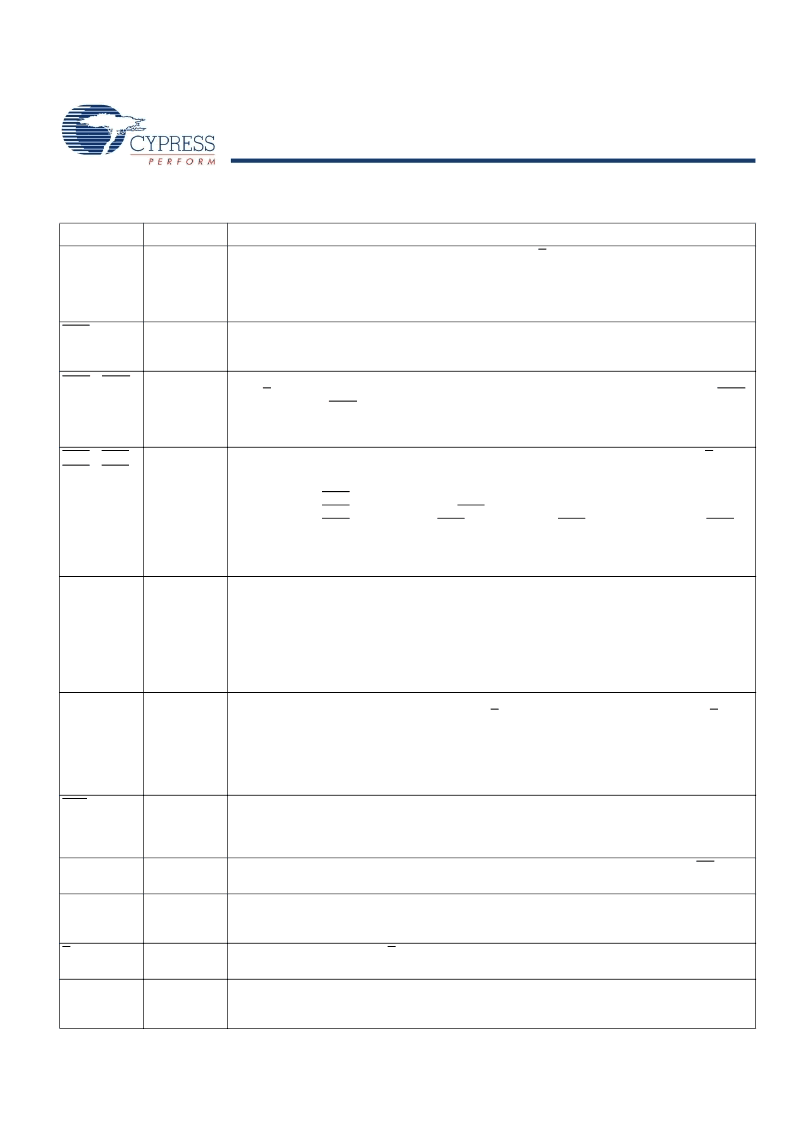

Pin Definitions

Pin Name

IO

Pin Description

D

[x:0]

Input-

Synchronous

Data Input Signals

. Sampled on the rising edge of K and K clocks during valid write operations.

CY7C1161V18

D

[7:0]

CY7C1176V18

D

[8:0]

CY7C1163V18

D

[17:0]

CY7C1165V18

D

[35:0]

Write Port Select

Active LOW

. Sampled on the rising edge of the K clock. When asserted active,

a write operation is initiated. Deasserting deselects the write port. Deselecting the write port causes

D

[x:0]

to be ignored.

Nibble Write Select 0, 1

Active LOW

(

CY7C1161V18

Only

). Sampled on the rising edge of the

K and K clocks during Write operations. Used to select the nibble that is written into the device. NWS

0

controls D

[3:0]

and NWS

1

controls D

[7:4]

.

All the nibble write selects are sampled on the same edge as the data. Deselecting a nibble write

select causes the corresponding nibble of data to be ignored and not written into the device.

WPS

Input-

Synchronous

NWS

0

, NWS

1

,

Input-

Synchronous

BWS

0

, BWS

1

,

BWS

2

, BWS

3

Input-

Synchronous

Byte Write Select 0, 1, 2, and 3

Active LOW

. Sampled on the rising edge of the K and K clocks

during write operations. Used to select the byte that is written into the device during the current portion

of the write operation. Bytes not written remain unaltered.

CY7C1176V18

BWS

0

controls D

[8:0].

CY7C1163V18

BWS

0

controls D

[8:0]

and BWS

1

controls D

[17:9]..

CY7C1165V18

BWS

0

controls D

[8:0]

, BWS

1

controls D

[17:9]

, BWS

2

controls D

[26:18],

and BWS

3

controls D

[35:27].

All the Byte Write Selects are sampled on the same edge as the data. Deselecting a Byte Write Select

causes the corresponding byte of data to be ignored and not written into the device.

A

Input-

Synchronous

Address Inputs

. Sampled on the rising edge of the K clock duing active read and write operations.

These address inputs are multiplexed for both read and write operations. Internally, the device is

organized as 2M x 8 (4 arrays each of 512K x 8) for CY7C1161V18, 2M x 9 (4 arrays each of 512K

x 9) for CY7C1176V18, 1M x 18 (4 arrays each of 256K x 18) for CY7C1163V18, and 512K x 36 (4

arrays each of 128K x 36) for CY7C1165V18. Therefore, only 19 address inputs are needed to access

the entire memory array of CY7C1161V18 and CY7C1176V18, 18 address inputs for CY7C1163V18,

and 17 address inputs for CY7C1165V18. These inputs are ignored when the appropriate port is

deselected.

Q

[x:0]

Outputs-

Synchronous

Data Output Signals

. These pins drive out the requested data during a read operation. Valid data

is driven out on the rising edge of both the K and K clocks during read operations or K and K when

in single clock mode. When the read port is deselected, Q

[x:0]

are automatically tri-stated.

CY7C1161V18

Q

[7:0].

CY7C1176V18

Q

[8:0].

CY7C1163V18

Q

[17:0].

CY7C1165V18

Q

[35:0].

Read Port Select

Active LOW

. Sampled on the rising edge of positive input clock (K). When active,

a read operation is initiated. Deasserting causes the read port to be deselected. When deselected,

the pending access is enabled to complete and the output drivers are automatically tri-stated following

the next rising edge of the K clock. Each read access consists of a burst of four sequential transfers.

RPS

Input-

Synchronous

QVLD

Valid Output

Indicator

Valid Output Indicator

. Indicates valid output data. QVLD is edge-aligned with CQ and CQ.

K

Input-

Clock

Positive Input Clock Input

. Rising edge of K is used to capture synchronous inputs to the device

and to drive out data through Q

[x:0]

when in single clock mode. All accesses are initiated on the rising

edge of K.

K

Input-

Clock

Negative Input Clock Input

. K is used to capture synchronous inputs presented to the device and

to drive out data through Q

[x:0]

when in single clock mode.

CQ

Echo Clock

Synchronous Echo Clock Outputs

. This is a free running clock and is synchronized to the input

clock (K) of the QDR-II+. The timings for the echo clocks are shown in

“Switching Characteristics”

on page 23

.

[+] Feedback

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C1176V18-300BZXC | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.5 Cycle Read Latency) |

| CY7C1176V18-300BZXI | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.5 Cycle Read Latency) |

| CY7C1176V18-333BZC | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.5 Cycle Read Latency) |

| CY7C1176V18-333BZI | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.5 Cycle Read Latency) |

| CY7C1176V18-333BZXC | 18-Mbit QDR⑩-II+ SRAM 4-Word Burst Architecture (2.5 Cycle Read Latency) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C1214F-100AC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1214F-100ACT | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1215F-166AC | 制造商:Rochester Electronics LLC 功能描述:1MB (32K X 32) 3.3V PIPELINE SCD - Bulk 制造商:Cypress Semiconductor 功能描述: |

| CY7C1215H-166AXC | 制造商:Cypress Semiconductor 功能描述:SRAM SYNC SGL 3.3V 1MBIT 32KX32 3.5NS 100TQFP - Bulk |

| CY7C1217H-133AXC | 制造商:Cypress Semiconductor 功能描述:SRAM SYNC QUAD 3.3V 1.125MBIT 32KX36 7.5NS 100TQFP - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。