- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄352929 > CY7C101-35PC x4 SRAM PDF資料下載

參數(shù)資料

| 型號: | CY7C101-35PC |

| 英文描述: | x4 SRAM |

| 中文描述: | x4的SRAM |

| 文件頁數(shù): | 1/9頁 |

| 文件大?。?/td> | 194K |

| 代理商: | CY7C101-35PC |

128K x 8 Static RAM

CY7C1019B/

CY7C10191B

Cypress Semiconductor Corporation

3901 North First Street

San Jose

CA 95134

408-943-2600

Document #: 38-05026 Rev. *A

Revised August 13, 2002

C1019V33

Features

High speed

—tAA = 10, 12, 15 ns

CMOS for optimum speed/power

Center power/ground pinout

Automatic power-down when deselected

Easy memory expansion with CE and OE options

Functionally equivalent to CY7C1019

Functional Description

The CY7C1019B/10191B is a high-performance CMOS static

RAM organized as 131,072 words by 8 bits. Easy memory

expansion is provided by an active LOW Chip Enable (CE), an

active LOW Output Enable (OE), and three-state drivers. This

device has an automatic power-down feature that significantly

reduces power consumption when deselected.

Writing to the device is accomplished by taking Chip Enable

(CE) and Write Enable (WE) inputs LOW. Data on the eight I/O

pins (I/O0 through I/O7) is then written into the location speci-

fied on the address pins (A0 through A16).

Reading from the device is accomplished by taking Chip

Enable (CE) and Output Enable (OE) LOW while forcing Write

Enable (WE) HIGH. Under these conditions, the contents of

the memory location specified by the address pins will appear

on the I/O pins.

The eight input/output pins (I/O0 through I/O7) are placed in a

high-impedance state when the device is deselected (CE

HIGH), the outputs are disabled (OE HIGH), or during a write

operation (CE LOW, and WE LOW).

The CY7C1019B/10191B is available in standard 32-pin

TSOP Type II and 400-mil-wide SOJ packages. Customers

should use part number CY7C10191B when ordering parts

with 10 ns tAA, and CY7C1019B when ordering 12 and 15 ns

tAA.

14

15

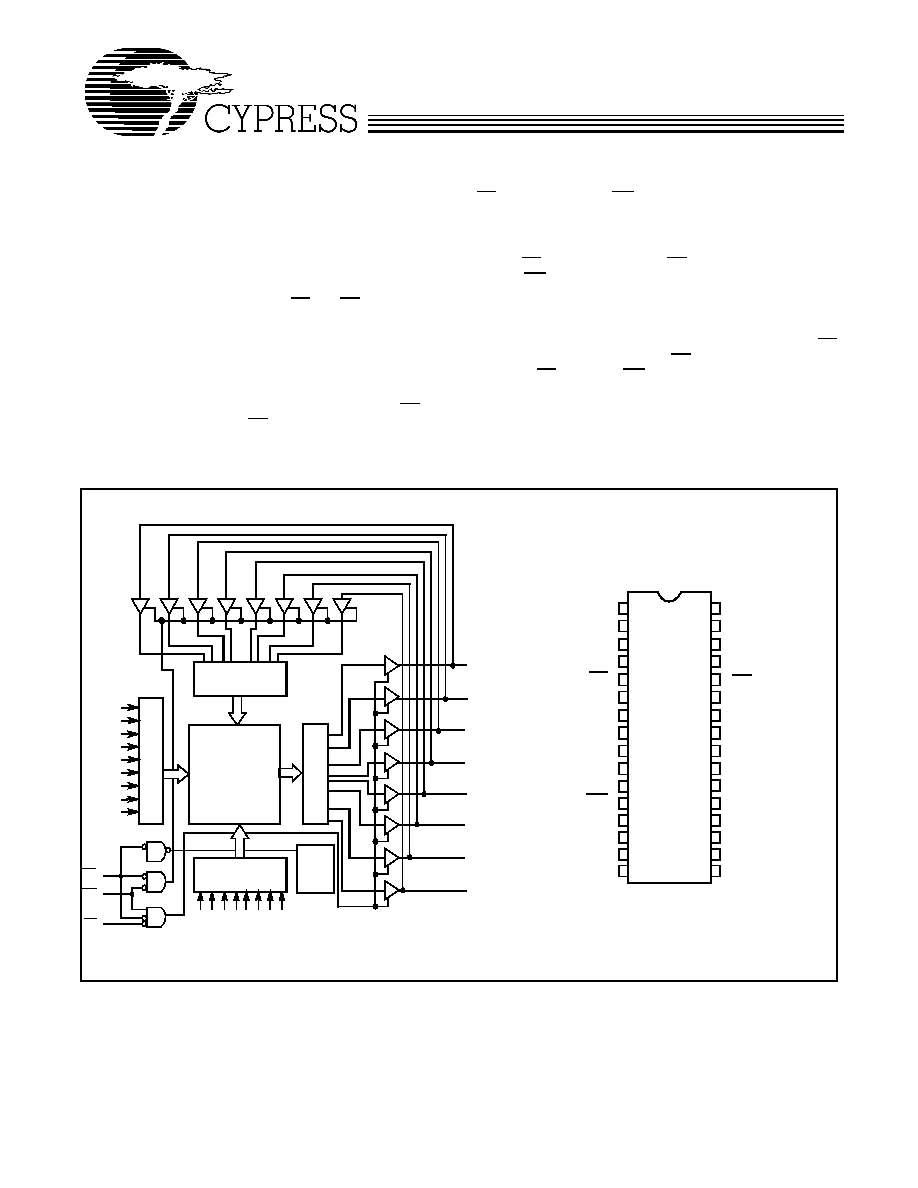

ogic Block Diagram

Pin Configurations

A1

A2

A3

A4

A5

A6

A7

A8

COLUMN

DECODER

ROW

DEC

O

D

E

R

SE

NSE

A

M

PS

INPUT BUFFER

POWER

DOWN

WE

OE

I/O0

I/O1

I/O2

I/O3

512 x 256 x 8

ARRAY

I/O7

I/O6

I/O5

I/O4

A0

A

11

A

13

A

12

A

10

CE

A

16

A

9

1

2

3

4

5

6

7

8

9

10

11

14

19

20

24

23

22

21

25

28

27

26

Top View

SOJ

12

13

29

32

31

30

16

15

17

18

A7

A1

A2

A3

CE

I/O0

I/O1

VCC

A13

A16

A

OE

I/O7

I/O6

A12

A11

A10

A9

I/O2

A0

A4

A5

A6

4

VCC

I/O5

A8

I/O3

WE

VSS

A14

V

SS

/ TSOPII

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C101-35VC | x4 SRAM |

| CY7C101-45DC | x4 SRAM |

| CY7C1019BV33-12VC | x8 SRAM |

| CY7C1019BV33-15VC | x8 SRAM |

| CY7C1019V33L-10VC | x8 SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C1014BNV33L-12ZXC | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1016D-10VXI | 制造商:Cypress Semiconductor 功能描述: |

| CY7C1018BV33-12VC | 制造商:Cypress Semiconductor 功能描述:SRAM Chip Async Single 3.3V 1M-Bit 128K x 8 12ns 32-Pin SOJ 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY7C1018BV33-12VCT | 制造商:Cypress Semiconductor 功能描述:SRAM Chip Async Single 3.3V 1M-Bit 128K x 8 12ns 32-Pin SOJ T/R 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel |

| CY7C1018BV33-15VI | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Cypress Semiconductor 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。