- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359518 > CY7C025AV-20AC (CYPRESS SEMICONDUCTOR CORP) 3.3V 4K/8K/16K x 16/18 Dual-Port Static RAM PDF資料下載

參數(shù)資料

| 型號(hào): | CY7C025AV-20AC |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | DRAM |

| 英文描述: | 3.3V 4K/8K/16K x 16/18 Dual-Port Static RAM |

| 中文描述: | 8K X 16 DUAL-PORT SRAM, 20 ns, PQFP100 |

| 封裝: | PLASTIC, TQFP-100 |

| 文件頁(yè)數(shù): | 10/19頁(yè) |

| 文件大小: | 241K |

| 代理商: | CY7C025AV-20AC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)當(dāng)前第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)

CY7C024AV/025AV/026AV

CY7C0241AV/0251AV/036AV

Document #: 38-06052 Rev. *E

Page 10 of 19

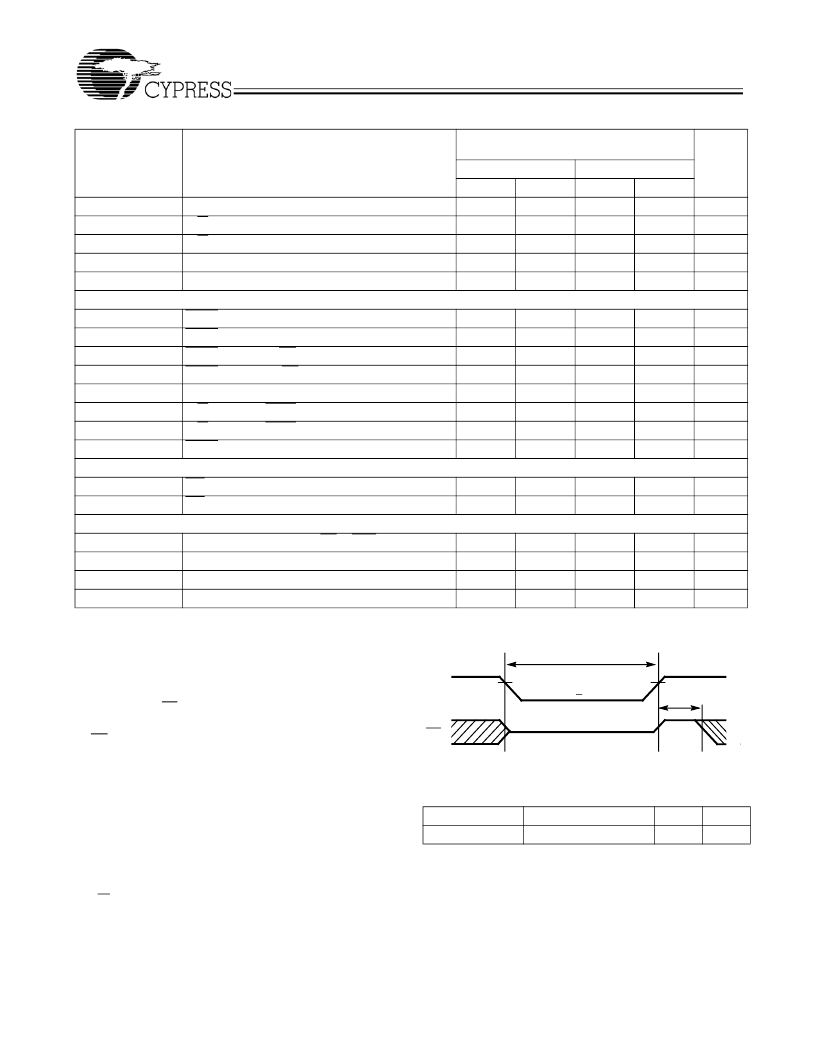

Data Retention Mode

The CY7C024AV/025AV/ 026AV and CY7C0241AV/ 0251AV/

036AV are designed with battery backup in mind. Data

retention voltage and supply current are guaranteed over

temperature. The following rules ensure data retention:

1. Chip Enable (CE) must be held HIGH during data retention,

within V

CC

to V

CC

– 0.2V.

2. CE must be kept between V

CC

– 0.2V and 70% of V

CC

during the power-up and power-down transitions.

3. The RAM can begin operation >t

RC

after V

CC

reaches the

minimum operating voltage (3.0V).

Notes:

23. For information on port-to-port delay through RAM cells from writing port to reading port, refer to Read Timing with Busy waveform.

24. Test conditions used are Load 2.

25. t

is a calculated parameter and is the greater of t

–t

(actual) or t

–t

(actual).

26. CE = V

CC

, V

in

= GND to V

CC

, T

A

= 25

°

C. This parameter is guaranteed but not tested.

t

HD

t

HZWE[21, 22]

t

LZWE[21, 22]

t

WDD[23]

t

DDD[23]

Busy Timing

[24]

t

BLA

t

BHA

t

BLC

t

BHC

t

PS

t

WB

t

WH

t

BDD[25]

Interrupt Timing

[24]

t

INS

t

INR

Semaphore Timing

t

SOP

t

SWRD

t

SPS

t

SAA

Data Hold From Write End

R/W LOW to High Z

R/W HIGH to Low Z

Write Pulse to Data Delay

Write Data Valid to Read Data Valid

0

0

ns

ns

ns

ns

ns

12

15

3

0

45

30

50

35

BUSY LOW from Address Match

BUSY HIGH from Address Mismatch

BUSY LOW from CE LOW

BUSY HIGH from CE HIGH

Port Set-up for Priority

R/W HIGH after BUSY (Slave)

R/W HIGH after BUSY HIGH (Slave)

BUSY HIGH to Data Valid

20

20

20

17

20

20

20

17

ns

ns

ns

ns

ns

ns

ns

ns

5

0

15

5

0

17

20

25

INT Set Time

INT Reset Time

20

20

20

20

ns

ns

SEM Flag Update Pulse (OE or SEM)

SEM Flag Write to Read Time

SEM Flag Contention Window

SEM Address Access Time

10

5

5

12

5

5

ns

ns

ns

ns

20

25

Switching Characteristics

Over the Operating Range (continued)

[18]

Parameter

Description

CY7C024AV/025AV/026AV

CY7C0241AV/0251AV/036AV

-20

Min.

Max.

Unit

-25

Min.

Max.

Timing

Parameter

ICC

DR1

Test Conditions

[26]

@ VCC

DR

= 2V

Max.

50

Unit

μ

A

Data Retention Mode

3.0V

3.0V

V

CC

>

2.0V

V

CC

to V

CC

– 0.2V

V

CC

CE

t

RC

VIH

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY7C145AV-20JC | 3.3V 4K/8K/16K/32K x 8/9 Dual-Port Static RAM |

| CY7C025AV-25AC | 3.3V 4K/8K/16K x 16/18 Dual-Port Static RAM |

| CY7C145AV-25JC | 3.3V 4K/8K/16K/32K x 8/9 Dual-Port Static RAM |

| CY7C1360B-166AC | CONNECTOR ACCESSORY |

| CY7C1360B-166AI | CONNECTOR ACCESSORY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY7C025AV-20AI | 制造商:Cypress Semiconductor 功能描述: |

| CY7C025AV-20AXC | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 3.3V 8Kx16 COM Async Dual Port 靜態(tài)隨機(jī)存取存儲(chǔ)器 RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問(wèn)時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| CY7C025AV-20AXI | 功能描述:IC SRAM 128KBIT 20NS 100LQFP RoHS:是 類別:集成電路 (IC) >> 存儲(chǔ)器 系列:- 標(biāo)準(zhǔn)包裝:1,000 系列:- 格式 - 存儲(chǔ)器:RAM 存儲(chǔ)器類型:移動(dòng) SDRAM 存儲(chǔ)容量:256M(8Mx32) 速度:133MHz 接口:并聯(lián) 電源電壓:1.7 V ~ 1.95 V 工作溫度:-40°C ~ 85°C 封裝/外殼:90-VFBGA 供應(yīng)商設(shè)備封裝:90-VFBGA(8x13) 包裝:帶卷 (TR) 其它名稱:557-1327-2 |

| CY7C025AV-25AC | 制造商:Rochester Electronics LLC 功能描述: 制造商:Cypress Semiconductor 功能描述: |

| CY7C025AV-25ACKJ | 制造商:Cypress Semiconductor 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。