- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄380135 > CY39200V676-125BBI (Cypress Semiconductor Corp.) CPLDs at FPGA Densities PDF資料下載

參數(shù)資料

| 型號(hào): | CY39200V676-125BBI |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | CPLDs at FPGA Densities |

| 中文描述: | CPLD器件在FPGA的密度 |

| 文件頁數(shù): | 86/86頁 |

| 文件大小: | 1235K |

| 代理商: | CY39200V676-125BBI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁當(dāng)前第86頁

Delta39K ISR

CPLD Family

Document #: 38-03039 Rev. *H

Page 86 of 86

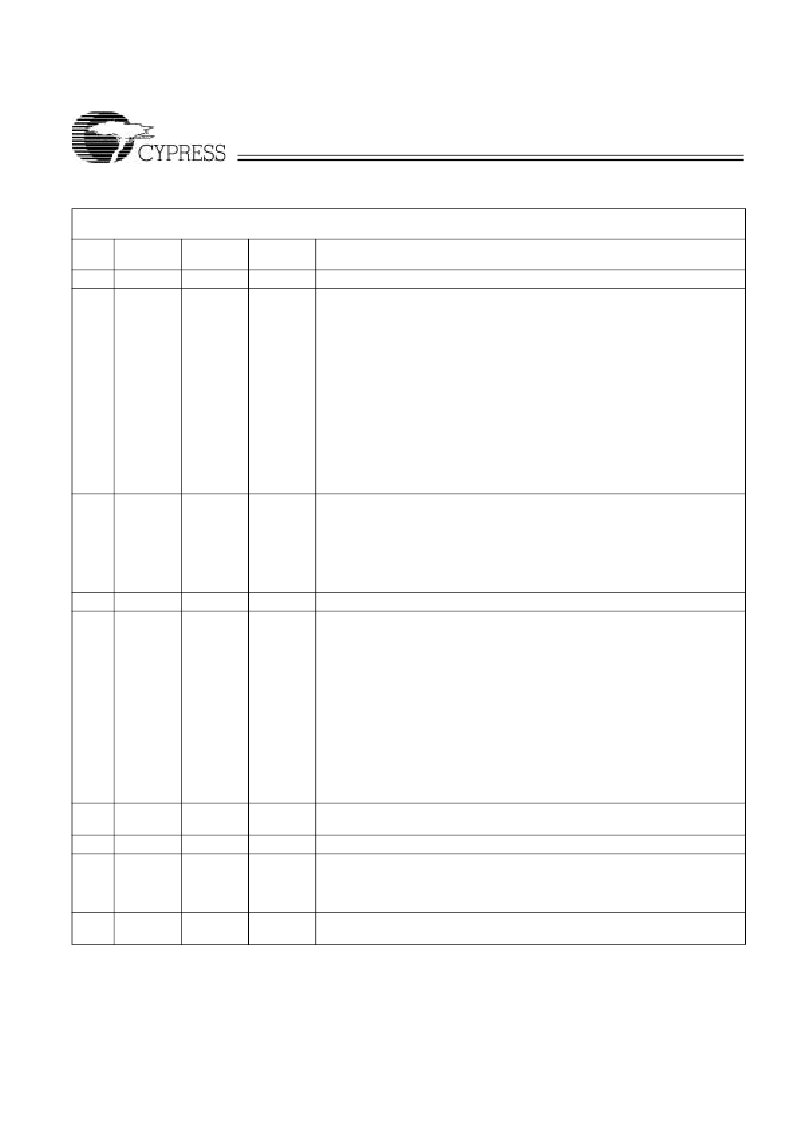

Document History Page

Document Title: Delta39K ISR CPLD Family CPLDs at FPGA Densities

Document Number: 38-03039

Issue

Date

**

106503

05/30/01

SZV

*A

107625

07/11/01

RN

REV.

ECN NO.

Orig. of

Description of Change

Change from Spec #: 38-00830 to 38-03039

Deleted 39K15 device and the associated -250-MHz bin specs

Deleted 144FBGA package and associated part numbers

Changed ESD spec from “MIL-STD-883” to “JEDEC EIA/JESD22-A114-A”

Changed the Prime bin for 39K50 and 39K30 from “MHz” to “233 MHz”

Changed the part ordering information accordingly

Updated the -233-MHz timing specs to match modified timing specs achieved by

design (main affected params: t

PD

, t

MCCO

, t

IOS

, t

SCS

, t

SCS2

, f

MAX2

, t

CLMAA

,

t

CLMCYC2

, t

CHMCYC2

, t

CHMCLK

)

Updated I/O standard Timing Delay Specs and changed the default I/O standard

from 3.3V PCI to LVCMOS

Added paragraph about Delta39K being CompactPCI hot swap Ready

Added X8 mode in the PLL description

Added Standby ICC spec

Updated the recommended boot PROM for 39K165/200 to be CY3LV002 instead

of CY3LV020

Updated Delta39K family offering

Modified PLL timing parameters t

DWSA

, t

DWOSA

, t

MCCJ

, and t

LOCK

. Added t

INDUTY

parameter

Deleted exception to CompactPCI Hot Swap compliance regarding “PCI

buffers....”

Added reference to app note “Hot Socketing Delta39K”

Revised CompactPCI Hot Swap Specification R1.0 to be R2.0

Combined with spec# 38-03040

Updated pin tables for 39K30 (208PQFP, 256FBGA)

Updated pin tables for 39K50 (208PQFP, 256/484FBGA, 388BGA)

Added X3, X5, X6, X16 multiplication modes to Spread Aware PLL

Added PLL parameters (f

PLLVCO

, P

SAPLLI

, f

MPPLI

)

Added and updated Storage Temperature for 39K200-208EQFP

Changed the I

cc0

spec for 39K165 and 39K200

Updated tCLZ, tCHMCYC2 parameter Values for -233 MHz bin

Updated

Input and Output Standard Timing Delay Adjustment

table

Removed Self Boot Industrial parts from the offering

Removed Delta39K165Z (1.8V) from the offering

Removed 144-FBGA package offering

Added self-boot Flash Memory endurance and data retention data

Added Family, Package, and Density Migration section

Added note 20 to 484/676 FBGA pin table to identify slow 39K165 IOs

Changed data sheet status from Preliminary to Final

Added note 7 to DC Characteristics

Updated spec 51-85103 (MG388 package drawing) to rev. *C

Changed the definition of following pins on CY39030 -256FBGA package:

Pin A10: From

IO/Vref7

to

IO/Vref6

Pin B7: From

IO/Vref6

to

V

CC

Added Table to identify Bank Location of Global Clock and Global Control Pins

Removed all “Z” parts (1.8V)

Referenced EEPROM to ATMEL part number

*B

109681

11/16/01

RN

*C

*D

112376

112946

12/21/01

04/04/02

RN

RN

*E

117518

10/04/02

OOR

*F

*G

121063

122543

11/06/02

12/10/02

DSG

RN

*H

128684

08/04/03

OOR

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY39200V676-125BGC | CPLDs at FPGA Densities |

| CY39200V676-125BGI | CPLDs at FPGA Densities |

| CY39200V676-200NTC | CPLDs at FPGA Densities |

| CY39200V676-200NTI | CPLDs at FPGA Densities |

| CY39200V676-233BBC | CPLDs at FPGA Densities |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY39200V676-125MBXC | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 Delta39K 200K 125MHz COM RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| CY39200V676-181MBC | 制造商:Cypress Semiconductor 功能描述: |

| CY39200V676-181MBXC | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 Delta39K 200K 181MHz COM RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| CY39200V676-83MBXC | 功能描述:CPLD - 復(fù)雜可編程邏輯器件 Delta39K 200K 83MHz COM RoHS:否 制造商:Lattice 系列: 存儲(chǔ)類型:EEPROM 大電池?cái)?shù)量:128 最大工作頻率:333 MHz 延遲時(shí)間:2.7 ns 可編程輸入/輸出端數(shù)量:64 工作電源電壓:3.3 V 最大工作溫度:+ 90 C 最小工作溫度:0 C 封裝 / 箱體:TQFP-100 |

| CY39200Z208-125BBC | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。