- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄380141 > CY39050V208-83BGC (Cypress Semiconductor Corp.) CPLDs at FPGA Densities PDF資料下載

參數(shù)資料

| 型號(hào): | CY39050V208-83BGC |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | CPLDs at FPGA Densities |

| 中文描述: | CPLD器件在FPGA的密度 |

| 文件頁(yè)數(shù): | 47/86頁(yè) |

| 文件大小: | 1235K |

| 代理商: | CY39050V208-83BGC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)當(dāng)前第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)

Delta39K ISR

CPLD Family

Document #: 38-03039 Rev. *H

Page 47 of 86

12

13

14

15

16

17

18

19

20

IO0

IO0

IO0

IO0

IO0

IO0

IO0

IO0

IO0

IO0

IO0

IO0

IO0

IO0

IO0

IO0

IO0

IO0

IO0

IO0

IO/V

REF0

IO0

IO0

IO0

V

CCIO0

IO0

IO0

V

CC

GND

NC

NC

IO/V

REF0

V

CCIO0

V

CCIO1

IO/V

REF1

IO1

IO1

IO1

IO1

V

CCIO1

GND

IO1

IO1

IO1

IO/V

REF1

IO1

IO1

IO1

IO1

V

CCPRG

V

CCIO1

GND

IO1

IO/V

REF1

IO1

IO1

V

CCCNFG

Data

Config_Done

Reset

IO/V

REF0

IO0

IO0

IO0

V

CCIO0

IO0

IO0

V

CC

GND

NC

NC

IO/V

REF0

V

CCIO0

V

CCIO1

IO/V

REF1

IO1

IO1

IO1

IO1

V

CCIO1

GND

IO1

IO1

IO1

IO/V

REF1

IO1

IO1

IO1

IO1

V

CCPRG

V

CCIO1

GND

IO1

IO/V

REF1

IO1

IO1

V

CCCNFG

Data

Config_Done

Reset

IO/V

REF0

IO0

IO0

IO0

V

CCIO0

IO0

IO0

V

CC

GND

V

CC

GND

IO/V

REF0

V

CCIO0

V

CCIO1

IO/V

REF1

IO1

IO1

IO1

IO1

V

CCIO1

GND

IO1

IO1

IO1

IO/V

REF1

IO1

IO1

IO1

IO1

V

CCPRG

V

CCIO1

GND

IO1

IO/V

REF1

IO1

IO1

V

CCCNFG

Data

Config_Done

Reset

IO/V

REF0

IO0

IO0

IO0

V

CCIO0

IO0

IO0

V

CC

GND

V

CC

GND

IO/V

REF0

V

CCIO0

V

CCIO1

IO/V

REF1

IO1

IO1

IO1

IO1

V

CCIO1

GND

IO1

IO1

IO1

IO/V

REF1

IO1

IO1

IO1

IO1

V

CCPRG

V

CCIO1

GND

IO1

IO/V

REF1

IO1

IO1

V

CCCNFG

Data

Config_Done

Reset

IO/V

REF0

IO0

IO0

IO0

V

CCIO0

IO0

IO0

V

CC

GND

V

CC

GND

IO/V

REF0

V

CCIO0

V

CCIO1

IO/V

REF1

IO1

IO1

IO1

IO1

V

CCIO1

GND

IO1

IO1

IO1

IO/V

REF1

IO1

IO1

IO1

IO1

V

CCPRG

V

CCIO1

GND

IO1

IO/V

REF1

IO1

IO1

V

CCCNFG

Data

Config_Done

Reset

21

[19]

22

[19]

23

24

25

26

27

[19]

28

29

30

[19]

31

[19]

32

[19]

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

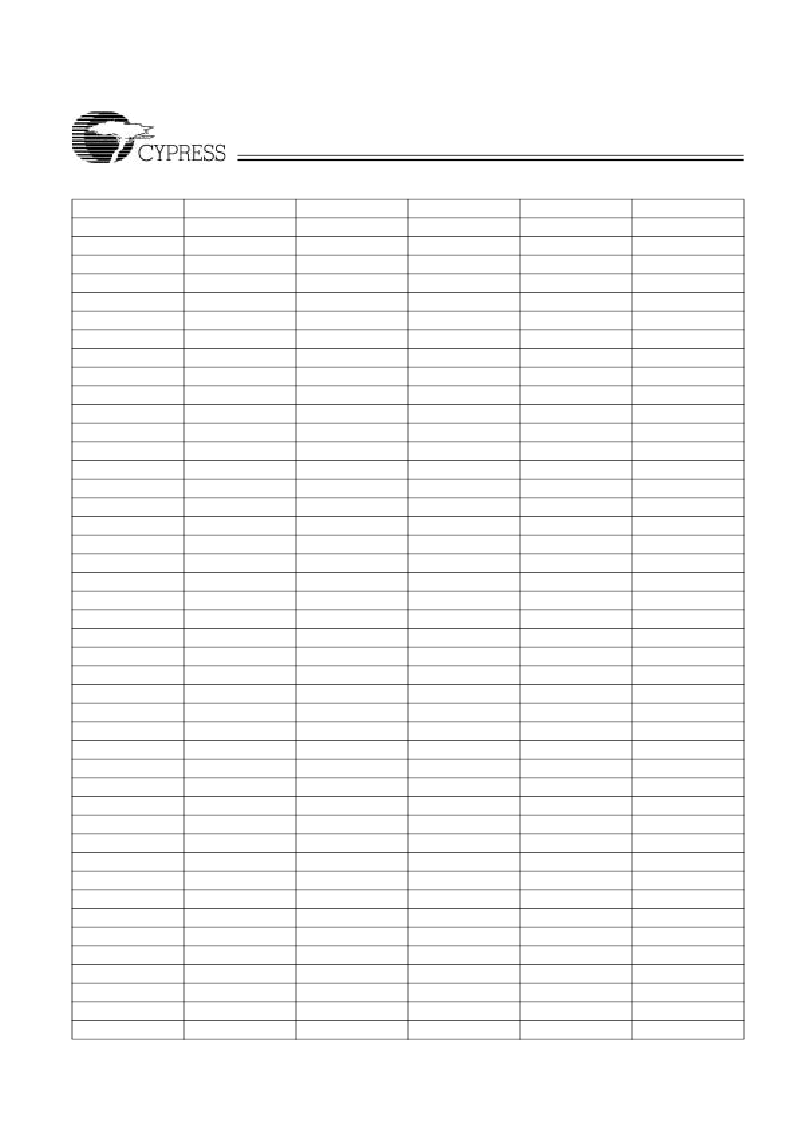

Table 11. 208 EQFP/PQFP Pin Table

(continued)

Pin

CY39030

CY39050

CY39100

CY39165

CY39200

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY39050V208-83BGI | CPLDs at FPGA Densities |

| CY39050V208-83MBC | Evaluation Board for ADL5602 - 50 MHz to 4.0 GHz RF/IF Gain Block |

| CY39050V208-83MBI | 50 MHz to 4.0 GHz RF/IF Gain Block; Package: 3-pin; Temperature Range: -40°C to +125°C |

| CY39050V208-83MGC | CPLDs at FPGA Densities |

| CY39050V208-83MGI | CPLDs at FPGA Densities |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY39050V208-83NTXC | 功能描述:IC CPLD 50K GATE 208BQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - CPLD(復(fù)雜可編程邏輯器件) 系列:Delta 39K™ ISR™ 標(biāo)準(zhǔn)包裝:24 系列:CoolRunner II 可編程類型:系統(tǒng)內(nèi)可編程 最大延遲時(shí)間 tpd(1):7.1ns 電壓電源 - 內(nèi)部:1.7 V ~ 1.9 V 邏輯元件/邏輯塊數(shù)目:24 宏單元數(shù):384 門(mén)數(shù):9000 輸入/輸出數(shù):173 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:208-BFQFP 供應(yīng)商設(shè)備封裝:208-PQFP(28x28) 包裝:托盤(pán) |

| CY39050V208-83NTXI | 功能描述:IC CPLD 50K GATE 208BQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - CPLD(復(fù)雜可編程邏輯器件) 系列:Delta 39K™ ISR™ 標(biāo)準(zhǔn)包裝:24 系列:CoolRunner II 可編程類型:系統(tǒng)內(nèi)可編程 最大延遲時(shí)間 tpd(1):7.1ns 電壓電源 - 內(nèi)部:1.7 V ~ 1.9 V 邏輯元件/邏輯塊數(shù)目:24 宏單元數(shù):384 門(mén)數(shù):9000 輸入/輸出數(shù):173 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:208-BFQFP 供應(yīng)商設(shè)備封裝:208-PQFP(28x28) 包裝:托盤(pán) |

| CY39050V484-125BBC | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

| CY39050V484-125BBI | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

| CY39050Z208-125BBC | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:CPLDs at FPGA Densities |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。