- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384268 > CY26113 Clocks and Buffers PDF資料下載

參數(shù)資料

| 型號(hào): | CY26113 |

| 英文描述: | Clocks and Buffers |

| 中文描述: | 時(shí)鐘和緩沖器 |

| 文件頁數(shù): | 3/5頁 |

| 文件大小: | 50K |

| 代理商: | CY26113 |

CY26111

Document #: 38-07095 Rev. *A

Page 3 of 5

DC Electrical Characteristics

AC Electrical Characteristics

Parame-

ter

[1]

I

OH

I

OL

I

OH

I

OL

V

IH

V

IL

C

IN

I

IZ

I

VDD

I

VDDL

I

VDDL

Name

Description

Min.

12

12

8

8

0.7

Typ.

24

24

16

16

Max.

Unit

mA

mA

mA

mA

V

DD

V

DD

pF

μ

A

mA

mA

mA

Output High Current

Output Low Current

Output High Current

Output Low Current

Input High Voltage

Input Low Voltage

Input Capacitance

Input Leakage Current

Supply Current

Supply Current

Supply Current

V

OH

= V

DD

–

0.5, V

DD

/V

DDL

= 3.3V

V

OL

= 0.5, V

DD

/V

DDL

= 3.3V

V

OH

= V

DDL

–

0.5, V

DDL

= 2.5V

V

OL

= 0.5, V

DDL

= 2.5V

CMOS levels, 70% of V

DD

CMOS levels, 30% of V

DD

OE Pin

OE Pin

AV

DD

/V

DD

Current

V

DDL

Current (V

DDL

=3.6V)

V

DDL

Current (V

DDL

= 2.625V)

0.3

7

5

30

10

8

Parameter

[1]

DC

Name

Description

Min.

40

Typ.

50

Max.

60

Unit

%

Duty Cycle is defined in Figure 1; t1/t2, 50% of

V

DD

t

3

Rising Edge Slew Rate Output Clock Rise Time, 20%

–

80% of

V

DD

/V

DDL

= 3.3V

Rising Edge Slew Rate Output Clock Rise Time, 20%

–

80% of

V

DDL

= 2.5V

Falling Edge Slew

Rate

V

DD

/V

DDL

= 3.3V

Falling Edge Slew

Rate

V

DDL

= 2.5V

Skew

Delay between related outputs at rising edge

Clock Jitter

Peak to Peak period jitter

PLL Lock Time

0.8

1.4

V/ns

t

3

0.6

1.2

V/ns

t

4

Output Clock Fall Time, 80%

–

20% of

0.8

1.4

V/ns

t

4

Output Clock Fall Time, 80%

–

20% of

0.6

1.2

V/ns

t5

t9

t10

200

250

3

ps

ps

ms

Note:

2.

Not 100% tested.

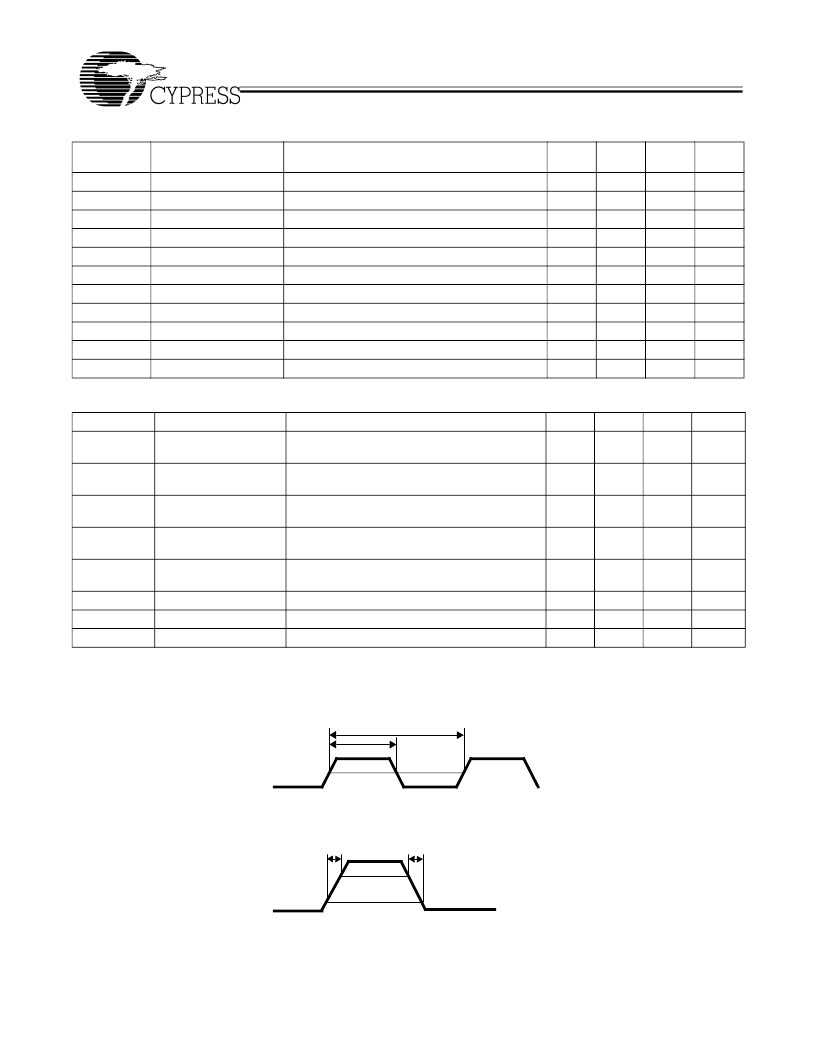

Figure 1. Duty Cycle Definition; DC = t2/t1.

Figure 2. Rise and Fall Time Definitions.

t1

t2

CLK

50%

50%

t3

CLK

80%

20%

t4

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY26113ZC | MISCELLANEOUS CLOCK GENERATOR|CMOS|TSSOP|16PIN|PLASTIC |

| CY26118 | Clocks and Buffers |

| CY26126 | Clocks and Buffers |

| CY26187-1 | Clocks and Buffers |

| CY26187-2 | Clocks and Buffers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY26113ZC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:MISCELLANEOUS CLOCK GENERATOR|CMOS|TSSOP|16PIN|PLASTIC |

| CY26114 | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:One-PLL Clock Generator |

| CY26114KZC | 功能描述:鎖相環(huán) - PLL One-PLL Clock Gen RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| CY26114KZCT | 功能描述:鎖相環(huán) - PLL One-PLL Clock Gen RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| CY26114ZC | 功能描述:鎖相環(huán) - PLL PacketClock COM RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。