- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378480 > CY22392ZC (Cypress Semiconductor Corp.) Three-PLL General Purpose FLASH Programmable Clock Generator PDF資料下載

參數(shù)資料

| 型號(hào): | CY22392ZC |

| 廠商: | Cypress Semiconductor Corp. |

| 英文描述: | Three-PLL General Purpose FLASH Programmable Clock Generator |

| 中文描述: | 三鎖相環(huán)通用閃存可編程時(shí)鐘發(fā)生器 |

| 文件頁數(shù): | 5/8頁 |

| 文件大?。?/td> | 157K |

| 代理商: | CY22392ZC |

CY22392

Document #: 38-07013 Rev. *D

Page 5 of 8

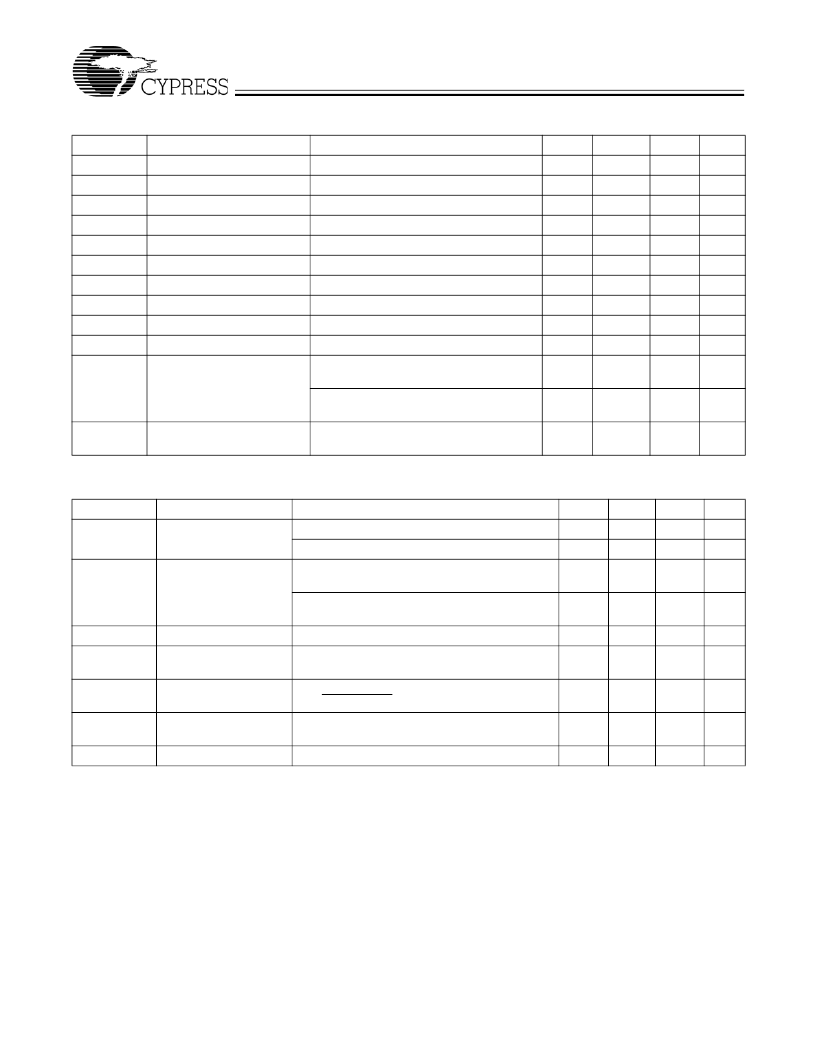

Electrical Characteristics

Parameter

Description

Conditions

Min.

Typ.

Max.

Unit

I

OH

I

OL

C

XTAL_MIN

C

XTAL_MAX

C

LOAD_IN

V

IH

V

IL

I

IH

I

IL

I

OZ

I

DD

Output High Current

[3]

Output Low Current

[3]

Crystal Load Capacitance

[3]

Crystal Load Capacitance

[3]

Input Pin Capacitance

[3]

V

OH

= V

DD

– 0.5, V

DD

= 3.3 V

V

OL

= 0.5V, V

DD

= 3.3 V

Capload at minimum setting

12

24

–

mA

12

24

–

mA

–

6

–

pF

Capload at maximum setting

–

30

–

pF

Except crystal pins

–

7

–

pF

HIGH-Level Input Voltage

CMOS levels,% of AV

DD

CMOS levels,% of AV

DD

V

IN

= AV

DD

– 0.3 V

V

IN

= +0.3 V

Three-state outputs

70%

–

–

AV

DD

AV

DD

μ

A

μ

A

μ

A

LOW-Level Input Voltage

–

–

30%

Input HIGH Current

–

<1

10

Input LOW Current

–

<1

10

Output Leakage Current

–

10

Total Power Supply Current

3.3V Power Supply; 2 outputs @

166 MHz; 4 outputs @ 83 MHz

–

100

–

mA

3.3V Power Supply; 2 outputs @

20 MHz; 4 outputs @ 40 MHz

–

50

–

mA

I

DDS

Total Power Supply Current in

Shutdown Mode

Shutdown active

–

5

20

μ

A

Switching Characteristics

Parameter

Name

Description

Min.

Typ.

Max.

Unit

1/t

1

Output Frequency

[3, 4]

Clock output limit, Commercial

–

–

200

MHz

Clock output limit, Industrial

Duty cycle for outputs, defined as t

2

÷

t

1

,

Fout < 100 MHz, divider >= 2, measured at V

DD

/2

Duty cycle for outputs, defined as t

2

÷

t

1

,

Fout > 100 MHz or divider = 1, measured at V

DD

/2

–

–

166

MHz

t

2

Output Duty Cycle

[3, 5]

45%

50%

55%

40%

50%

60%

t

3

t

4

Rising Edge Slew Rate

[3]

Output clock rise time, 20% to 80% of V

DD

Falling Edge Slew

Rate

[3]

0.75

1.4

–

V/ns

Output clock fall time, 20% to 80% of V

DD

0.75

1.4

–

V/ns

t

5

Output three-state

Timing

[3]

Clock Jitter

[3, 6]

Time for output to enter or leave three-state mode

after SHUTDOWN/OE switches

–

150

300

ns

t

6

Peak-to-peak period jitter, CLK outputs measured

at V

DD

/2

PLL Lock Time from Power-up

–

400

–

ps

t

7

Lock Time

[3]

–

1.0

3

ms

Notes:

3. Guaranteed by design, not 100% tested.

4. Guaranteed to meet 20%–80% output thresholds and duty cycle specifications.

5. Reference Output duty cycle depends on XTALIN duty cycle.

6. Jitter varies significantly with configuration. Reference Output jitter depends on XTALIN jitter and edge rate.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY22392ZI | Three-PLL General Purpose FLASH Programmable Clock Generator |

| CY22392ZXC | Three-PLL General Purpose FLASH Programmable Clock Generator |

| CY22392ZXI | Three-PLL General Purpose FLASH Programmable Clock Generator |

| CY22392FI | Three-PLL General Purpose FLASH Programmable Clock Generator |

| CY22392FXC | Three-PLL General Purpose FLASH Programmable Clock Generator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY22392ZC-333 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY22392ZC-337 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY22392ZC-338 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY22392ZC-339 | 制造商:Rochester Electronics LLC 功能描述:FACTORY PROG CODE SPECIFIC 3-PLL CLK SYN. CUST#15-8851-01 - Bulk |

| CY22392ZC-347 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。