- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378998 > CY22313ZC (CYPRESS SEMICONDUCTOR CORP) Non-Insulated Male Tab PDF資料下載

參數(shù)資料

| 型號: | CY22313ZC |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | XO, clock |

| 英文描述: | Non-Insulated Male Tab |

| 中文描述: | 393.216 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO24 |

| 封裝: | 4.40 MM, TSSOP-24 |

| 文件頁數(shù): | 4/9頁 |

| 文件大小: | 165K |

| 代理商: | CY22313ZC |

CY22313

Document #: 38-07434 Rev. *E

Page 4 of 9

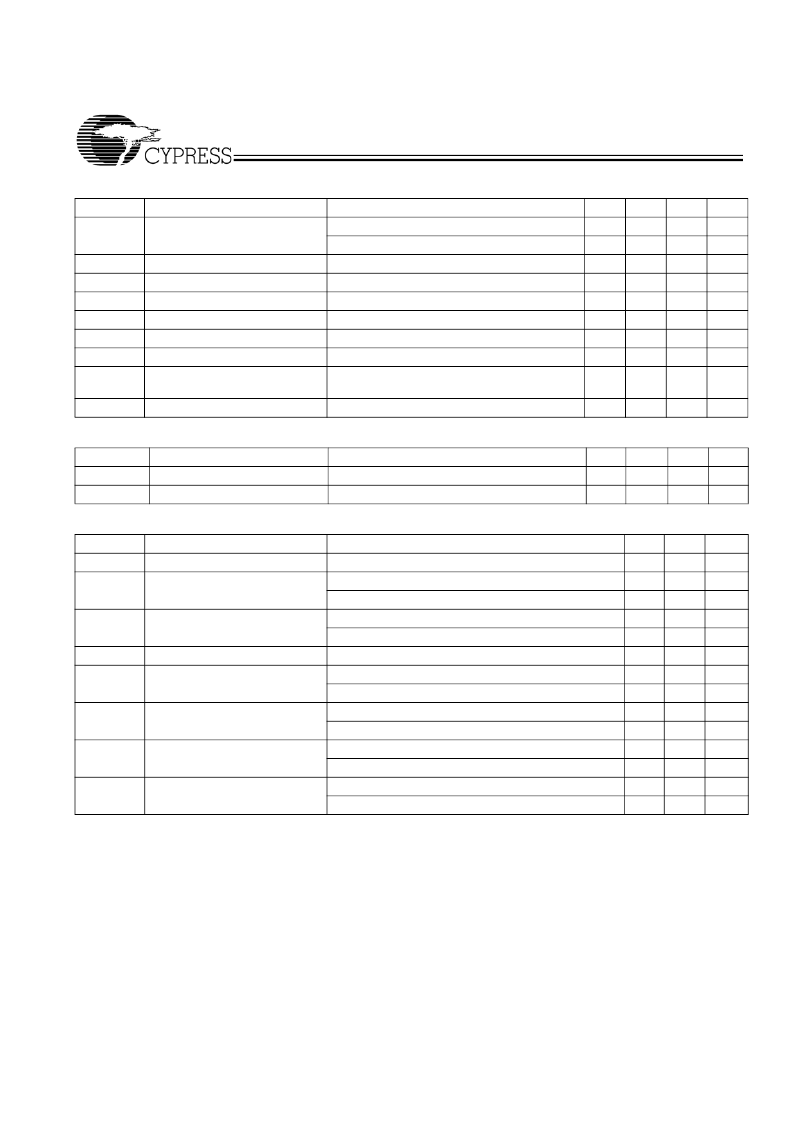

Switching Characteristics

[3]

Parameter

F

PPM

Description

Conditions

Min.

Typ.

±5

±2

50

1.2

0.5

1.2

0.5

Max.

±10

±5

55

4.0

2.5

4.0

2.5

400

100

Unit

PPM

PPM

%

V/ns

V/ns

V/ns

V/ns

ps

ps

Frequency Error

Part to Part, does not include PCB variation

[8]

Over commercial temperature range

[9]

Duty cycle for all outputs, measured at V

DD

/2

DC

t

3_54, 2.5

t

3_54, 1.675

t

4_54, 2.5

t

4_54, 1.675

t

CR

, t

CF

t

CR-CF

Output Duty Cycle

54MOUT Rising Edge Slew Rate 20% to 80% of V

DD54

, V

DD54

= 2.5V

54MOUT Rising Edge Slew Rate 20% to 80% of V

DD54

, V

DD54

= 1.675V

54MOUT Falling Edge Slew Rate 80% to 20% of V

DD54

, V

DD54

= 2.5V

54MOUT Falling Edge Slew Rate 80% to 20% of V

DD54

, V

DD54

= 1.675V

CLK/CLKB Rise and Fall Times

20% to 80% of output voltage

CLK/CLKB Rise and Fall

Difference

[10]

Lock Time

[11]

PLL lock time from power-up

45

0.75

0.35

0.75

0.35

160

20% to 80% of output voltage

t

5

1.0

3.0

ms

Phase Noise Specifications

Parameter

Description

Conditions

Min.

Typ.

–95

–92

Max.

Unit

dBc

dBc

Phase Noise

Phase Noise

54 MHz at 10-kHz offset

53.946 MHz at 10-kHz offset

Jitter Specifications

[3]

Parameter

t

6_LCLK

t

6_54, 2.5

Description

Conditions

Typ.

Max.

250

150

150

250

250

250

400

400

50

70

300

400

50

70

Unit

ps

ps

ps

ps

ps

ps

ps

ps

ps

ps

ps

ps

ps

ps

LCLK Jitter

[12]

54MOUT Jitter

[12]

Cycle-Cycle Jitter – 9.216 MHz

Cycle-Cycle Jitter – 54 MHz, V

DD

= 2.5V

Cycle-Cycle Jitter – 53.946 MHz, V

DD

= 2.5V

Cycle-Cycle Jitter – 54 MHz, V

DD

= 1.675V

Cycle-Cycle Jitter – 53.946 MHz, V

DD

= 1.675V

1000 Cycle Jitter – 9.216 MHz

1000 Cycle Jitter – 54 MHz,

1000 Cycle Jitter – 53.946 MHz,

Cycle-Cycle Jitter, 1–6 Cycles, 400 MHz

Cycle-Cycle Jitter, 1–6 Cycles, 300 MHz

Long-term Jitter, 400 MHz

Long-term Jitter, 300 MHz

Cycle-Cycle Duty Cycle Error, 400 MHz

Cycle-Cycle Duty Cycle Error, 300 MHz

t

6_54, 1.675

t

7_LCLK

t

7_54

LCLK 1000 Cycle Jitter

[13]

54MOUT 1000 Cycle Jitter

[13]

t

8

CLK/CLKB 1–6 Cycle Jitter

[14]

t

9

CLK/CLKB Long-term Jitter

[15]

t

10

CLK/CLKB Duty Cycle Error

[16]

Notes:

8.

9.

10. Crystal should not be heated for this test, only IC.

11.

Lock Time shown in

Figure 2.

12. LCLK and 54MOUT Cycle-Cycle Jitter shown in

Figure 3.

13. LCLK and 54MOUT 1000 Cycle Jitter shown in

Figure 4.

14. CLK/CLKB 1-6 Cycle Jitter specification is absolute value of worst case deviation, and is shown in

Figure 5

and

Figure 6

.

15. CLK/CLKB Long Term Jitter shown in

Figure 7

.

16. CLK/CLKB Duty Cycle Error shown in

Figure 8

.

Tested across three lots on same board, PCB boards can vary more than ± 5 PPM.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY22313ZCT | Non-Insulated Male Tab |

| CY22313ZXC | Vinyl Insulated Male Tab |

| CY22313ZXCT | Date Code 0007 |

| CY22393FC | -bit AVR Microcontroller with 8K Bytes In- System Programmable Flash |

| CY22393FIT | -bit AVR Microcontroller with 8K Bytes In- System Programmable Flash |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY22313ZC-1 | 功能描述:鎖相環(huán) - PLL 2PLL Clk Genratr COM RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| CY22313ZCT | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:Two-PLL Clock Generator with Direct Rambus-TM (Lite) Support |

| CY22313ZXC | 功能描述:鎖相環(huán) - PLL 2PLL Clk Genratr COM RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| CY22313ZXCT | 功能描述:鎖相環(huán) - PLL 2PLL Clk Genratr COM RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| CY22315ZXCT | 制造商:Cypress Semiconductor 功能描述:DEFAULT CATEGORY |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。