- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369674 > CT2556 (Aeroflex Inc.) CT2553 / 2554 / 2555 / 2556 Advanced Integrated MUX (AIM) Hybrid FOR MIL-STD-1553 PDF資料下載

參數(shù)資料

| 型號: | CT2556 |

| 廠商: | Aeroflex Inc. |

| 英文描述: | CT2553 / 2554 / 2555 / 2556 Advanced Integrated MUX (AIM) Hybrid FOR MIL-STD-1553 |

| 中文描述: | CT2553 / 2554 /二千五百五十六分之二千五百五十五高級集成復(fù)用器(AIM)的混合的MIL - STD - 1553的 |

| 文件頁數(shù): | 13/36頁 |

| 文件大?。?/td> | 352K |

| 代理商: | CT2556 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁

Aeroflex Circuit Technology

13

SCDCT2553 REV B 8/6/99 Plainview NY (516) 694-6700

BC OPERATION

Initialization of the CT2553 via a Reset or by

setting the appropriate Configuration Register bits

will result in placing the CT2553 in the BC

operating mode.

BC MEMORY CONFIGURATION

. The user

configures the memory by: (1) writing the start

address of the Descriptor Stack into the Current

Area Stack Point location; (2) loading the fourth

word of each Descriptor Stack Entry (DSE) with

the start location of each message block; and (3)

loading the Message Counter with the total

number of messages to be transmitted. Note that

the Message Count must be written in 1's

compliment. For example, to transmit one

message, load OOFE(H) (See Table 3, BC

Memory Map).

If both map areas A and B are utilized, this

procedure must be performed for each area. Note

that the Stack Pointer and Message Counter

locations are fixed; Message Block locations are

user-defined.

Each message block must be proceeded by a BC

Control Word (See Figure 14). This word informs

the CT2553 as to the format of the message

transfer. Bit 1 of the Control Word defines whether

the following message to RT 31 is to be issued in

Broadcast Mode or whether RT 31 is a unique

terminal. Memory locations must be reserved at

the end of each message for: (1) a Loop Back

Word; (2) RTU Status Word(s); and (3) received

Data words. See Figure 16, BC Message

Formats.

Message blocks may be loaded anywhere in the

non-fixed area of the shared RAM. However, each

data block may not cross a 256 word boundary

(i.e., bit 8 of the starting address of the message

block must match bit 8 of the address of the last

word of the message block).

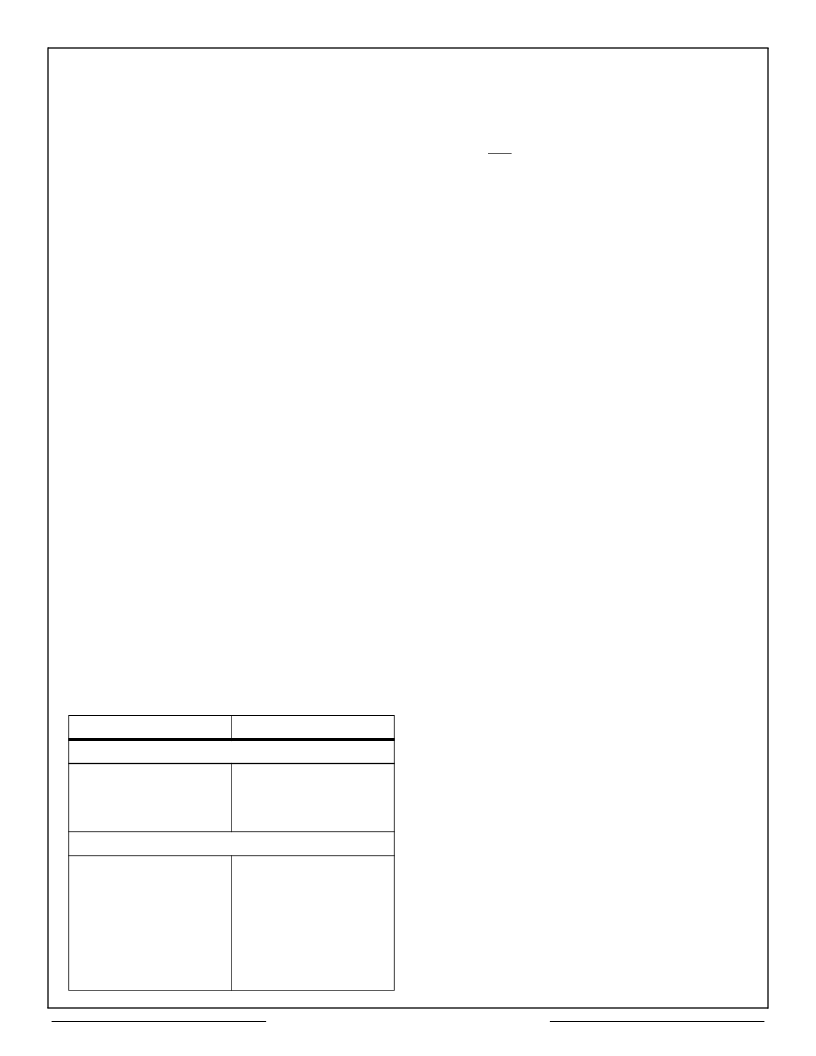

Table 3 - Typical BC Memory Map

ADDITIONAL FEATURES

. The Configuration

Register – STOP ON ERROR bit can be set. This

causes the CT2553 to halt operation at the end of

the current message transfer if an error is

detected. In addition, setting the Interrupt Mask

Register bits will result in a low pulse on the

Interrupt (INT) pin with each occurrence of the

respective error, end of message or end of

message frame condition (See Configuration

Register and Interrupt Register sections).

BC TRANSFER-START SEQUENCE

After setting the CONTROLLER START bit in the

following actions:

1. Reads the Current Area Stack Pointer for the

address of the Descriptor Stack Entry (DSE).

2. Stores an SOM (Start of Message) flag in the

Block Status word to indicate a transfer

operation in progress.

3. Writes the Time Tag value into the Descriptor

Stack (See Time Tag).

4. Reads the Data Block Address from the fourth

location of the DSE.

5. Starts the MIL-STD-1553 message transfer.

Upon completion of the MIL-STD-1553 message

transfer, the CT2553:

1. Generates an End Of Message (EOM) or Error

(if applicable) interrupt if enabled.

2. Reads the Stack Pointer for the address of the

DSE.

3. Updates the Block Status Word; resets SOM,

sets EOM, and sets any applicable Error bits.

4. Writes the Time Tag value into the Descriptor

Stack (See Time Tag).

5. Increment Pointers: Stack Pointer incremented

by 4 and Message Count incremented by 1.

6. If more messages remain to be sent, a BC End

Of Message (BCEOM) interrupt occurs (if

enabled).

If an error occurs and Stop On Error has been

enabled, the CT2553 stops initiating BC

Transfer-Start sequences. The Stack Pointer will

point to the next message to be transferred (See

Figure 17).

HEX ADDRESS

FUNCTION

Fixed Areas

0100

0101

0104

0105

Stack Pointer A

Message Count A

Stack Pointer B

Message Count B

User Defined Areas

0108-013F

0140-017F

0180-01BF

01C0-01FF

0F00-0FFF

0000-00FF

Not Used

Data Block 1

Data Block 2

Data Block 3

Descriptor Stack A

Descriptor Stack B

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CT2561 | CT2561 Bus Controller, Remote Terminal and BUS Monitor FOR MIL-STD-1553B |

| CT2561-FP | CT2561 Bus Controller, Remote Terminal and BUS Monitor FOR MIL-STD-1553B |

| CT2565-001-1 | CT2565 Bus Controller, Remote Terminal and BUS Monitor FOR MIL-STD-1553B |

| CT2565 | CT2565 Bus Controller, Remote Terminal and BUS Monitor FOR MIL-STD-1553B |

| CT2565-001-2 | CT2565 Bus Controller, Remote Terminal and BUS Monitor FOR MIL-STD-1553B |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CT2556-FP | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:CT2553 / 2554 / 2555 / 2556 Advanced Integrated MUX (AIM) Hybrid FOR MIL-STD-1553 |

| CT2561 | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:CT2561 Bus Controller, Remote Terminal and BUS Monitor FOR MIL-STD-1553B |

| CT2561-FP | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:CT2561 Bus Controller, Remote Terminal and BUS Monitor FOR MIL-STD-1553B |

| CT2565 | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:CT2565 Bus Controller, Remote Terminal and BUS Monitor FOR MIL-STD-1553B |

| CT2565-001-1 | 制造商:AEROFLEX 制造商全稱:AEROFLEX 功能描述:CT2565 Bus Controller, Remote Terminal and BUS Monitor FOR MIL-STD-1553B |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。