- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄223608 > COP8SGR928Q9 (National Semiconductor Corporation) 8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART PDF資料下載

參數(shù)資料

| 型號(hào): | COP8SGR928Q9 |

| 廠商: | National Semiconductor Corporation |

| 英文描述: | 8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

| 中文描述: | 8位的CMOS基于ROM和OTP微控制器具有8K到32K的內(nèi)存,2個(gè)比較器和USART |

| 文件頁(yè)數(shù): | 37/62頁(yè) |

| 文件大小: | 913K |

| 代理商: | COP8SGR928Q9 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)當(dāng)前第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)

11.0 WATCHDOG/Clock Monitor (Continued)

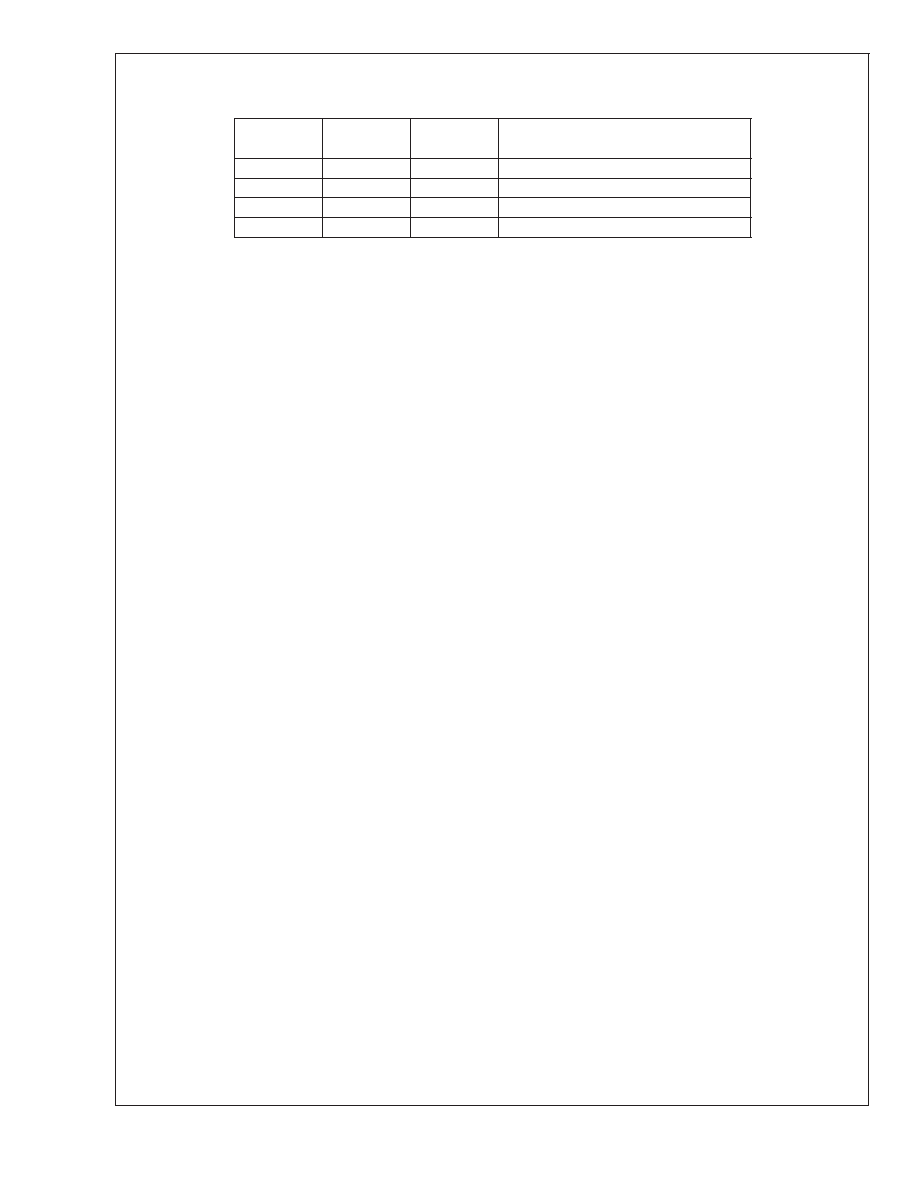

TABLE 9. WATCHDOG Service Actions

Key

Window

Clock

Action

Data

Monitor

Match

Valid Service: Restart Service Window

Don’t Care

Mismatch

Don’t Care

Error: Generate WATCHDOG Output

Mismatch

Don’t Care

Error: Generate WATCHDOG Output

Don’t Care

Mismatch

Error: Generate WATCHDOG Output

11.3 WATCHDOG AND CLOCK MONITOR SUMMARY

The following salient points regarding the WATCHDOG and

CLOCK MONITOR should be noted:

Both the WATCHDOG and CLOCK MONITOR detector

circuits are inhibited during RESET.

Following RESET, the WATCHDOG and CLOCK MONI-

TOR are both enabled, with the WATCHDOG having the

maximum service window selected.

The WATCHDOG service window and CLOCK MONI-

TOR enable/disable option can only be changed once,

during the initial WATCHDOG service following RESET.

The initial WATCHDOG service must match the key data

value in the WATCHDOG Service register WDSVR in

order to avoid a WATCHDOG error.

Subsequent WATCHDOG services must match all three

data fields in WDSVR in order to avoid WATCHDOG

errors.

The correct key data value cannot be read from the

WATCHDOG Service register WDSVR. Any attempt to

read this key data value of 01100 from WDSVR will read

as key data value of all 0’s.

The WATCHDOG detector circuit is inhibited during both

the HALT and IDLE modes.

The CLOCK MONITOR detector circuit is active during

both the HALT and IDLE modes. Consequently, the de-

vice inadvertently entering the HALT mode will be de-

tected as a CLOCK MONITOR error (provided that the

CLOCK MONITOR enable option has been selected by

the program).

With the single-pin R/C oscillator option selected and the

CLKDLY bit reset, the WATCHDOG service window will

resume following HALT mode from where it left off before

entering the HALT mode.

With the crystal oscillator option selected, or with the

single-pin R/C oscillator option selected and the CLKDLY

bit set, the WATCHDOG service window will be set to its

selected value from WDSVR following HALT. Conse-

quently, the WATCHDOG should not be serviced for at

least 2048 instruction cycles following HALT, but must be

serviced within the selected window to avoid a WATCH-

DOG error.

The IDLE timer T0 is not initialized with external RESET.

The user can sync in to the IDLE counter cycle with an

IDLE counter (T0) interrupt or by monitoring the T0PND

flag. The T0PND flag is set whenever the twelfth bit of the

IDLE counter toggles (every 4096 instruction cycles). The

user is responsible for resetting the T0PND flag.

A hardware WATCHDOG service occurs just as the de-

vice exits the IDLE mode. Consequently, the WATCH-

DOG should not be serviced for at least 2048 instruction

cycles following IDLE, but must be serviced within the

selected window to avoid a WATCHDOG error.

Following RESET, the initial WATCHDOG service (where

the service window and the CLOCK MONITOR enable/

disable must be selected) may be programmed any-

where within the maximum service window (65,536 in-

struction cycles) initialized by RESET. Note that this initial

WATCHDOG service may be programmed within the ini-

tial 2048 instruction cycles without causing a WATCH-

DOG error.

11.4 DETECTION OF ILLEGAL CONDITIONS

The device can detect various illegal conditions resulting

from coding errors, transient noise, power supply voltage

drops, runaway programs, etc.

Reading of undefined ROM gets zeroes. The opcode for

software interrupt is 00. If the program fetches instructions

from undefined ROM, this will force a software interrupt, thus

signaling that an illegal condition has occurred.

The subroutine stack grows down for each call (jump to

subroutine), interrupt, or PUSH, and grows up for each

return or POP. The stack pointer is initialized to RAM location

06F Hex during reset. Consequently, if there are more re-

turns than calls, the stack pointer will point to addresses 070

and 071 Hex (which are undefined RAM). Undefined RAM

from addresses 070 to 07F (Segment 0), and all other seg-

ments (i.e., Segments 4 … etc.) is read as all 1’s, which in

turn will cause the program to return to address 7FFF Hex. It

is recommended that the user either leave this location

unprogrammed or place an INTR instruction (all 0’s) in this

location to generate a software interrupt signaling an illegal

condition.

Thus, the chip can detect the following illegal conditions:

1.

Executing from undefined ROM.

2.

Over “POP”ing the stack by having more returns than

calls.

When the software interrupt occurs, the user can re-initialize

the stack pointer and do a recovery procedure before restart-

ing (this recovery program is probably similar to that follow-

ing reset, but might not contain the same program initializa-

tion procedures). The recovery program should reset the

software interrupt pending bit using the RPND instruction.

12.0 MICROWIRE/PLUS

MICROWIRE/PLUS is a serial SPI compatible synchronous

communications interface. The MICROWIRE/PLUS capabil-

ity enables the device to interface with MICROWIRE/PLUS

or SPI peripherals (i.e. A/D converters, display drivers, EE-

PROMs etc.) and with other microcontrollers which support

the MICROWIRE/PLUS or SPI interface. It consists of an

8-bit serial shift register (SIO) with serial data input (SI),

serial data output (SO) and serial shift clock (SK).

shows a block diagram of the MICROWIRE/PLUS logic.

The shift clock can be selected from either an internal source

or an external source. Operating the MICROWIRE/PLUS

COP8SG

Family

www.national.com

42

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| COP8SGR928V3 | 8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

| COP8SGR928V6 | 8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

| COP8SGR928V7 | 8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

| COP8SGR928V8 | 8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

| COP8SGR928V9 | 8-Bit CMOS ROM Based and OTP Microcontrollers with 8k to 32k Memory, Two Comparators and USART |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| COP8-SKFLASH-00 | 功能描述:開(kāi)發(fā)板和工具包 - 其他處理器 DEV STARTER KIT RoHS:否 制造商:Freescale Semiconductor 產(chǎn)品:Development Systems 工具用于評(píng)估:P3041 核心:e500mc 接口類(lèi)型:I2C, SPI, USB 工作電源電壓: |

| COP8-SKFLASH-01 | 功能描述:開(kāi)發(fā)板和工具包 - 其他處理器 COP8 5V FLASH STARTER KIT RoHS:否 制造商:Freescale Semiconductor 產(chǎn)品:Development Systems 工具用于評(píng)估:P3041 核心:e500mc 接口類(lèi)型:I2C, SPI, USB 工作電源電壓: |

| COP8-SW-COP8C | 制造商:NSC 制造商全稱(chēng):National Semiconductor 功能描述:8-Bit CMOS Flash Microcontroller with 8k Memory, Dual Op Amps, Virtual EEROM, Temperature Sensor,10-Bit A/D and Brownout Reset |

| COP8-SW-COP8CW | 制造商:NSC 制造商全稱(chēng):National Semiconductor 功能描述:8-Bit CMOS Flash Microcontroller with 8k Memory, Dual Op Amps, Virtual EEROM, Temperature Sensor,10-Bit A/D and Brownout Reset |

| COP8-SW-EWCOP8 | 制造商:NSC 制造商全稱(chēng):National Semiconductor 功能描述:8-Bit CMOS Flash Microcontroller with 8k Memory, Dual Op Amps, Virtual EEROM, Temperature Sensor,10-Bit A/D and Brownout Reset |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。