- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄352816 > COP820CP-1 8-BIT MICROCONTROLLER PDF資料下載

參數(shù)資料

| 型號: | COP820CP-1 |

| 元件分類: | 8位微控制器 |

| 英文描述: | 8-BIT MICROCONTROLLER |

| 中文描述: | 8位微控制器 |

| 文件頁數(shù): | 14/26頁 |

| 文件大小: | 352K |

| 代理商: | COP820CP-1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁

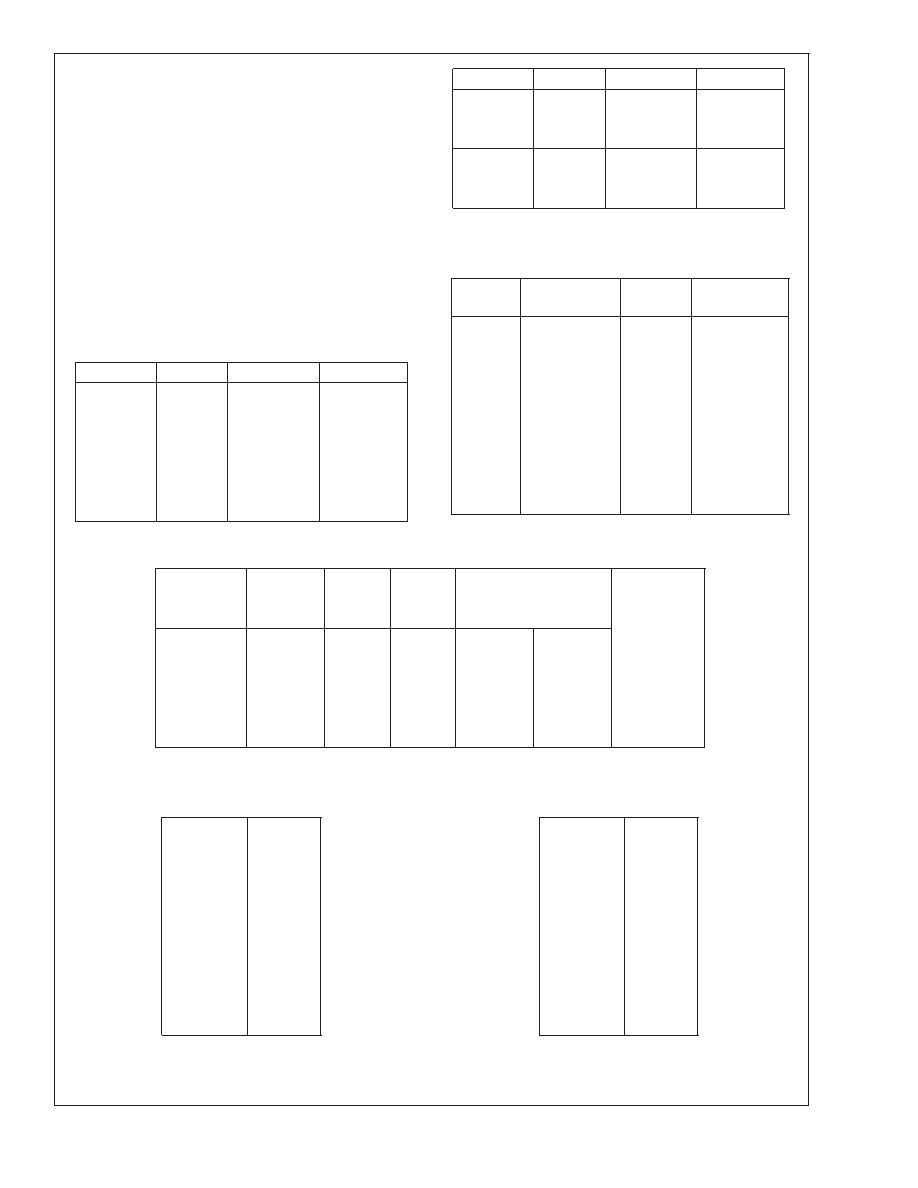

Instruction Execution Time

Most instructions are single byte (with immediate addressing

mode instruction taking two bytes).

Most single instructions take one cycle time to execute.

Skipped instructions require x number of cycles to be

skipped, where x equals the number of bytes in the skipped

instruction opcode.

See the BYTES and CYCLES per INSTRUCTION table for

details.

Bytes and Cycles per

Instruction

The following table shows the number of bytes and cycles for

each instruction in the format of byte/cycle.

Arithmetic and Logic Instructions

[B]

Direct

Immed.

ADD

1/1

3/4

2/2

ADC

1/1

3/4

2/2

SUBC

1/1

3/4

2/2

AND

1/1

3/4

2/2

OR

1/1

3/4

2/2

XOR

1/1

3/4

2/2

IFEQ

1/1

3/4

2/2

[B]

Direct

Immed.

IFGT

1/1

3/4

2/2

IFBNE

1/1

DRSZ

1/3

SBIT

1/1

3/4

RBIT

1/1

3/4

IFBIT

1/1

3/4

The following table shows the instructions assigned to un-

used opcodes. This table is for information only. The opera-

tions performed are subject to change without notice. Do not

use these opcodes.

Unused

Opcode

Instruction

Unused

Opcode

Instruction

60

NOP

A9

NOP

61

NOP

AF

LD A, [B]

62

NOP

B1

C → HC

63

NOP

B4

NOP

67

NOP

B5

NOP

8C

RET

B7

X A, [X]

99

NOP

B9

NOP

9F

LD [B], #i

BF

LDA,[X]

A7

X A, [B]

A8

NOP

Memory Transfer Instructions

Register

Register Indirect

Indirect

Direct

Immed.

Auto Incr & Decr

[B]

[X]

[B+, B]

[X+, X]

XA,*

1/1

1/3

2/3

1/2

1/3

LD A,*

1/1

1/3

2/3

2/2

1/2

1/3

LD B,Imm

1/1

(If B < 16)

LD B,Imm

2/3

(If B > 15)

LD Mem,Imm

2/2

3/3

2/2

LD Reg,Imm

2/3

Note 20: * = > Memory location addressed by B or X or directly.

Instructions Using A & C

CLRA

1/1

INCA

1/1

DECA

1/1

LAID

1/3

DCORA

1/1

RRCA

1/1

SWAPA

1/1

SC

1/1

RC

1/1

IFC

1/1

IFNC

1/1

Transfer of Control Instructions

JMPL

3/4

JMP

2/3

JP

1/3

JSRL

3/5

JSR

2/5

JID

1/3

RET

1/5

RETSK

1/5

RETI

1/5

INTR

1/7

NOP

1/1

COP820C/COP840C

www.national.com

21

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| COP820CP-2 | 8-BIT MICROCONTROLLER |

| COP820CP-3 | 8-BIT MICROCONTROLLER |

| COP820CP-4 | 8-BIT MICROCONTROLLER |

| COP820CP-5 | 8-BIT MICROCONTROLLER |

| COP840CP-1 | 8-BIT MICROCONTROLLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| COP820CP-2 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| COP820CP-3 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| COP820CP-4 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| COP820CP-5 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| COP820C-XXX/D | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。